SoC (system on chip) dynamic voltage frequency scaling method with foresight

A dynamic voltage and frequency adjustment technology, applied in the direction of data processing power supply, etc., can solve the problems of inability to achieve performance and power consumption, limited prediction, and inability to make accurate responses, so as to reduce power consumption and ensure performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

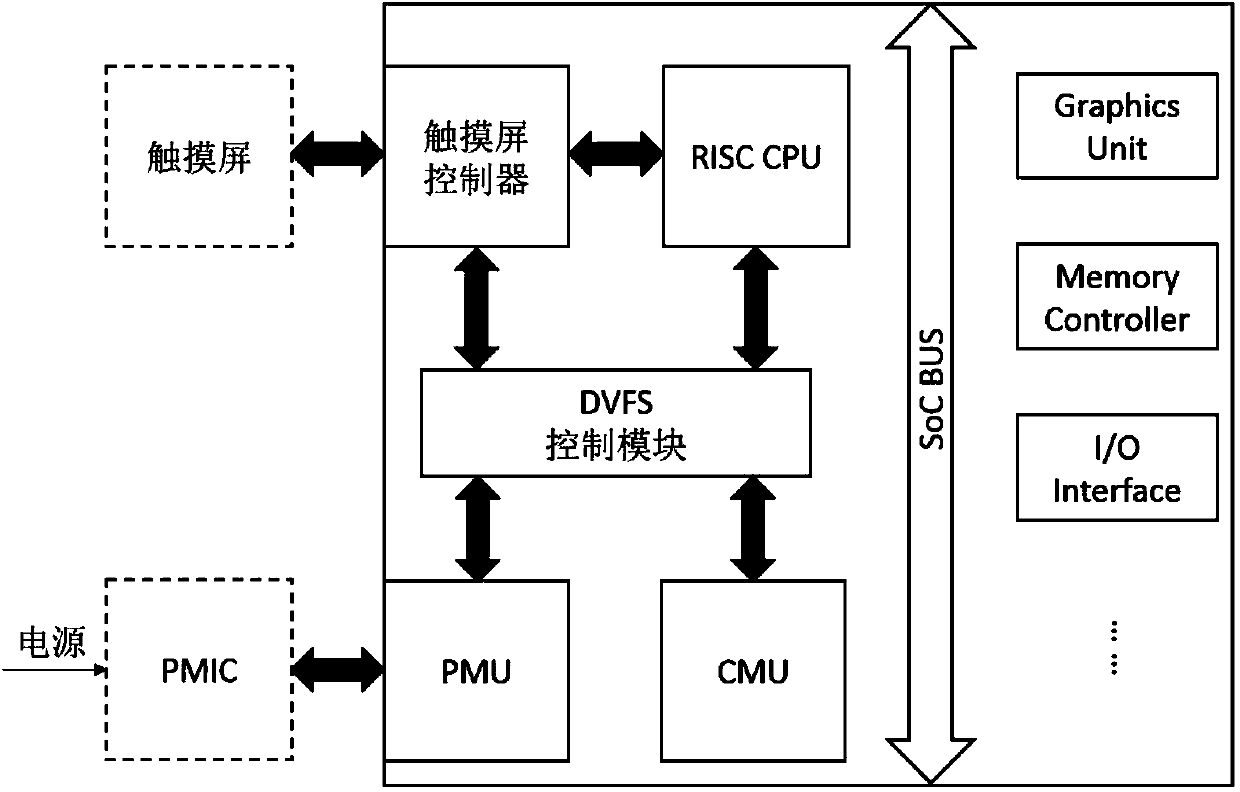

[0031] see figure 1 As shown, the SoC system architecture diagram adopting the method of the present invention, the SoC chip includes: a touch screen controller, a power management unit (PMU, Power Management Unit), a clock management unit (CMU, Clock Management Unit), a DVFS module, and a simplified instruction set Processor (RISC CPU), on-chip bus (SoC BUS), graphics unit (Graphics Unit), memory controller (Memory Controller), input and output interface module (I / O Interface), etc.; and the above-mentioned SoC system level The controller, unit or module contained in the chip adopts the form of IP core and is described in Verilog hardware description language.

[0032] The above SoC chip also manages the power consumption of the SoC system-on-chip through an external power management integrated circuit PMIC.

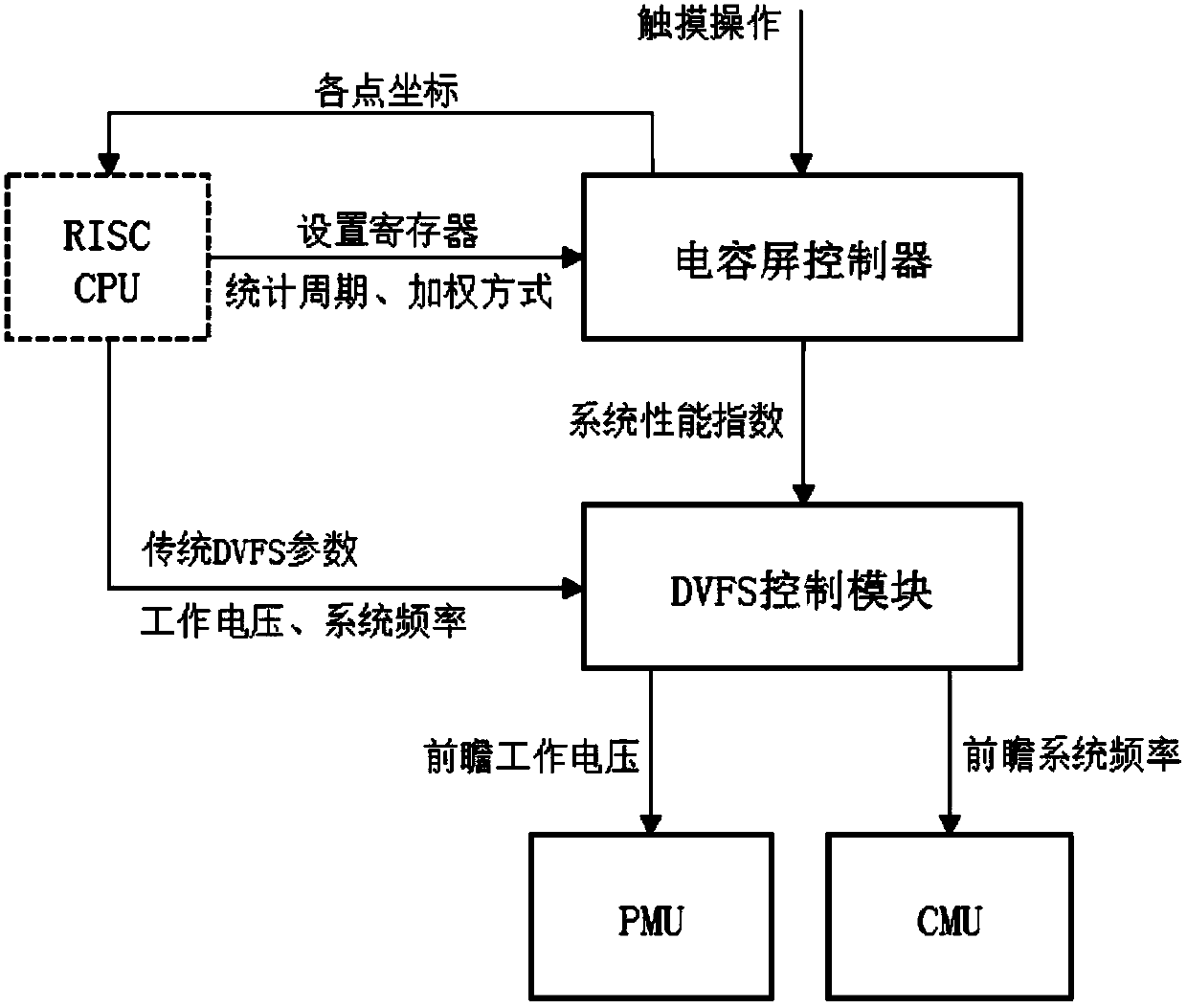

[0033] The working process of the present invention is described in detail below, see figure 2 Shown:

[0034] 1. After the SoC using this method is powered on, the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com