POP packaging structure

A technology of packaging structure and packaging body, which is applied in the direction of electrical components, electrical solid devices, circuits, etc., to achieve the effect of reducing warpage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

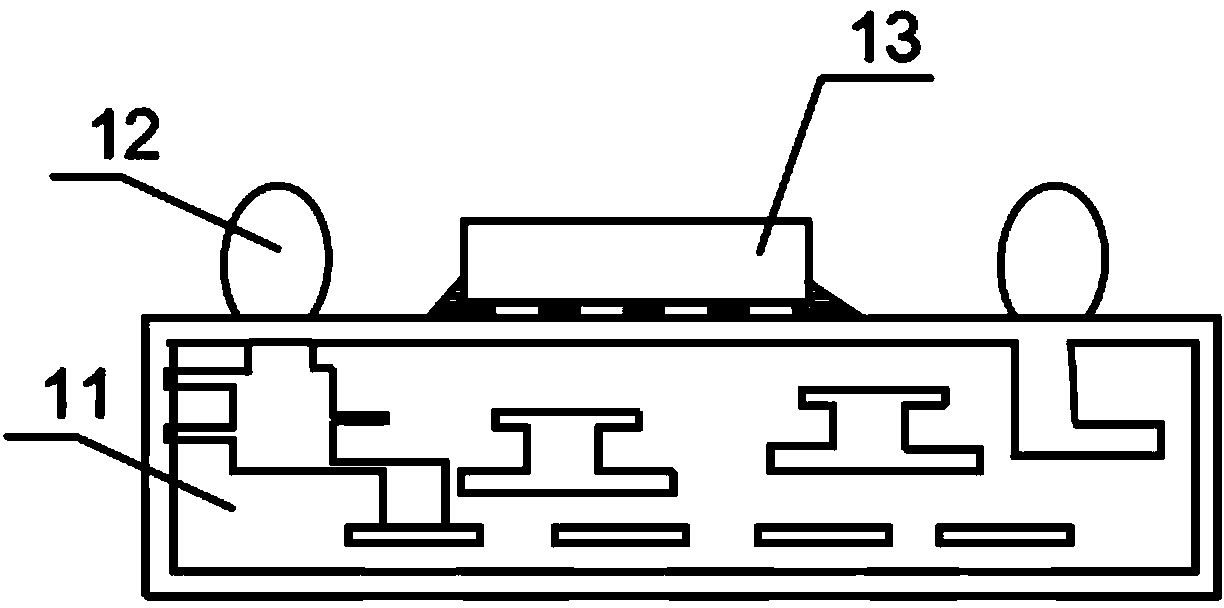

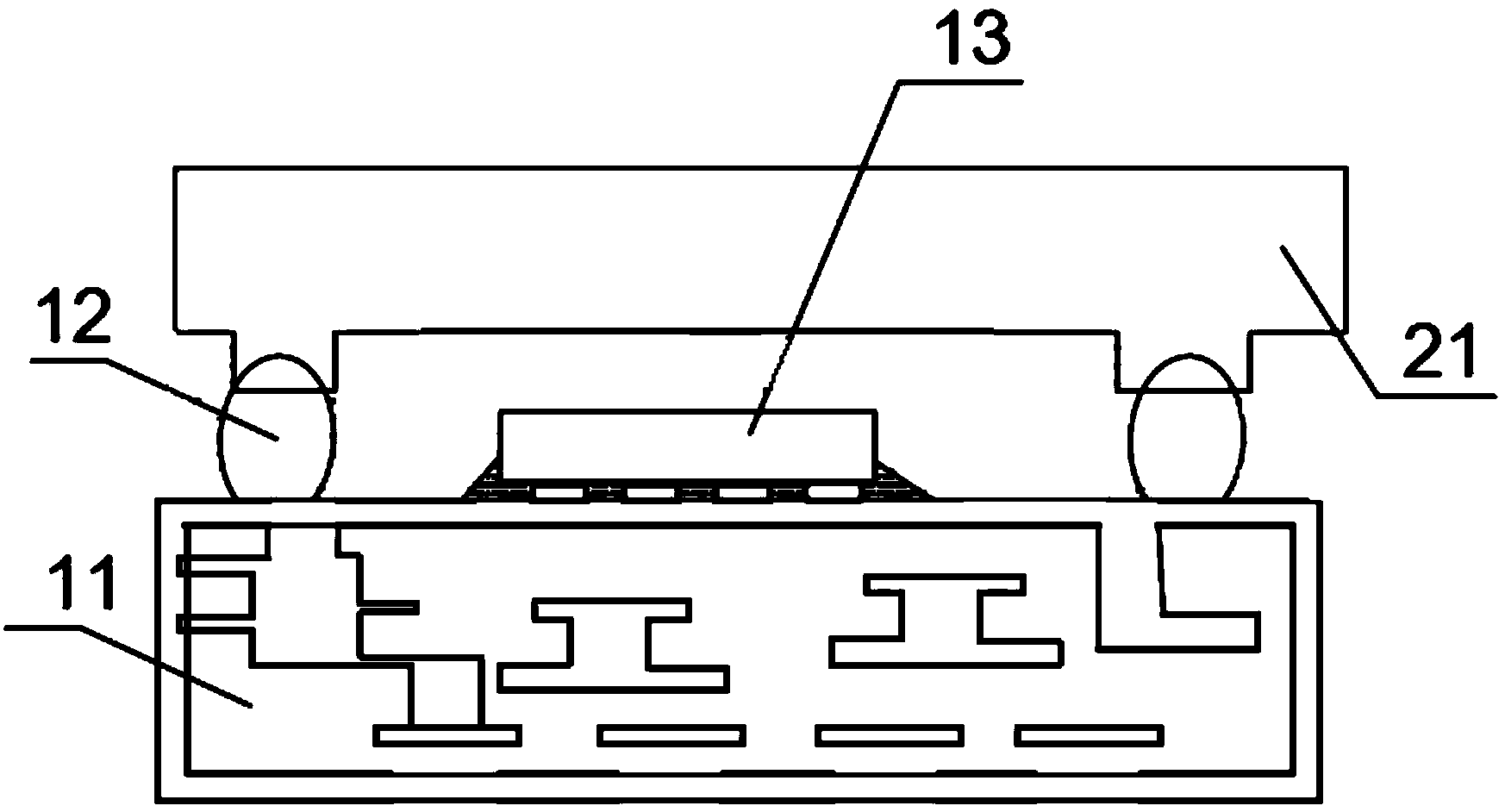

[0036] Such as figure 1 As shown, first, a substrate 11 is provided, a chip 13 is placed on the upper surface of the substrate 11, and the chip 13 is soldered on the substrate by a reflow soldering technique, and the chip 13 and the substrate 11 pass through the bottom Filling technology is used for reinforcement, and the underfilling can use molded underfilling technology or capillary underfilling technology.

[0037] Optionally, before the next step, a first solder ball 12 is formed on the upper surface of the substrate 11 or provided with a first solder ball on the surface of the substrate; the first solder ball on the upper surface of the substrate is used for contact with the upper package body Connect to realize the electrical interconnection between the upper package and the lower package. The first solder ball 12 on the upper surface of the substrate can be soldered on the upper surface of the substrate after the chip is packaged, or directly on the surface of the substrat...

Embodiment 2

[0046] Such as figure 1 As shown, first, a substrate 11 is provided, a chip 13 is placed on the upper surface of the substrate 11, and the chip 13 is soldered on the substrate by reflow soldering technology, and the chip 13 and the substrate 11 pass through the bottom Filling technology for reinforcement, where the underfilling can be molded underfilling technology or capillary underfilling technology; the first solder ball on the upper surface of the substrate can be set when the substrate is provided, or after the chip is soldered The upper surface of the substrate is provided with first solder balls.

[0047] Subsequently, a metal strip 31 is provided, and the metal strip is subjected to photolithography and / or etching to form Figure 7 In the shape shown, metal bumps are formed on one side of the metal strip, and windings are also formed on the side where the metal bumps are formed.

[0048] The side of the metal strip with bumps and windings is facing down to the substrate, an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com