A vacuum brazing chip mounting process method without load and low void ratio

A process method and low-void technology, applied in auxiliary devices, manufacturing tools, welding equipment, etc., can solve the problems of large void rate in chip loading, demanding chip requirements, easy to damage chips, etc., to improve brazing quality and yield , Reduce the brazing void rate, improve the effect of brazing quality

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0027] Step (1), solder selection

[0028] The sizes of the chips to be brazed are 1mm×1mm, 5mm×5mm, 10mm×10mm, respectively, and Au80Sn20 solder is selected.

[0029] Step (2), metallization on the back of the chip

[0030] The back of the chip to be brazed is metallized by sputtering Au process.

[0031] Step (3), film loading

[0032] Install the chip to be brazed on the gold-plated chip area to be brazed on the integrated circuit package shell, and put Au80Sn20 solder between the chip to be soldered and the gold-plated chip area to be brazed;

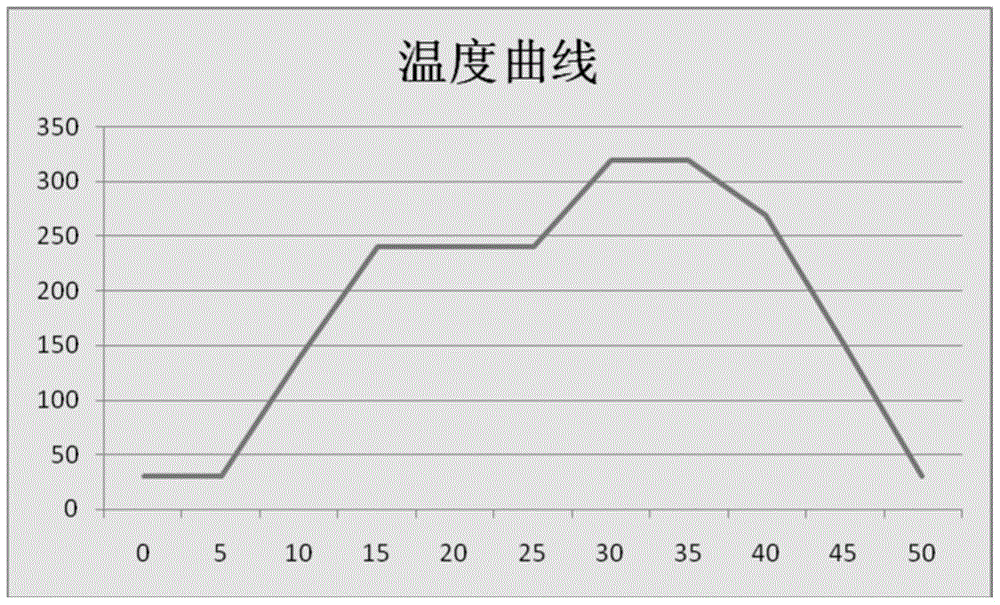

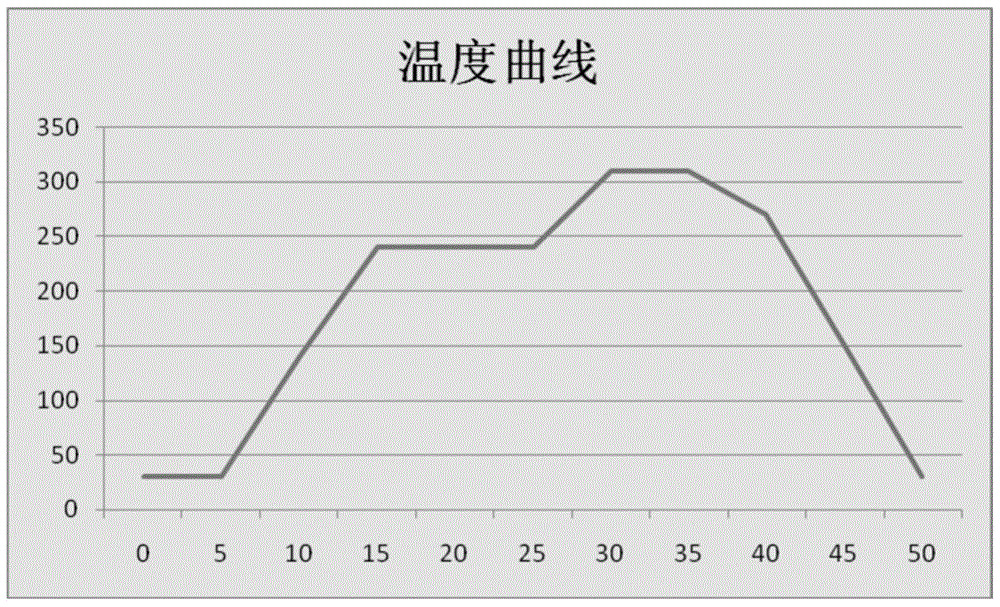

[0033] Step (4), place the sample to be welded in vacuum brazing equipment for brazing, the specific process is as follows:

[0034] (1) From room temperature (generally 15-30°C) to 180°C, the heating rate is 1°C / s, and the temperature is kept for 4 minutes;

[0035] (2), continue to heat up to 220 ° C, the heating rate is 1 ° C / s, vacuumize, so that the vacuum in the brazing equipment is reduced to <0.001mbar;

[0036] (3), ...

Embodiment 2

[0043] Step (1), solder selection

[0044] The size of the chip to be brazed is 1mm×1mm, 5mm×5mm, 10mm×10mm respectively, and Pb92.5Sn2.5Ag5 solder is selected.

[0045] Step (2), metallization on the back of the chip

[0046] The back of the chip to be brazed is metallized by sputtering Au process.

[0047] Step (3), film loading

[0048] The chip to be brazed is installed in the gold-plated area to be brazed of the integrated circuit package shell, and Pb92.5Sn2.5Ag5 solder is put between the chip to be soldered and the gold-plated area to be brazed;

[0049] Step (4), place the sample to be welded in vacuum brazing equipment for brazing, the specific process is as follows:

[0050] (1) From room temperature to 176°C, the heating rate is 1.5°C / s, and the temperature is kept for 5 minutes;

[0051] (2) Continue to heat up to 218°C with a heating rate of 1.5°C / s, and vacuumize to reduce the vacuum in the brazing equipment to <0.001mbar;

[0052] (3), continue to heat up t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com