Semiconductor structure and forming method thereof

A technology of semiconductor and ring structure, which is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve the problems of high cost and low efficiency of chip manufacturing process, and achieve process cost saving, process step saving, The effect of improving process efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] After discovery and analysis, in the prior art, the method of fixing and supporting the thinned wafer makes the entire chip manufacturing process inefficient and the reasons for the high cost are as follows:

[0040] In the prior art, there are mainly two methods for fixing and supporting the wafer during the chip manufacturing process.

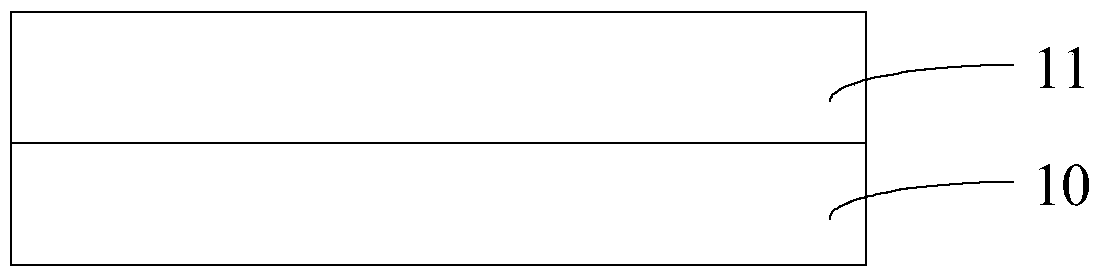

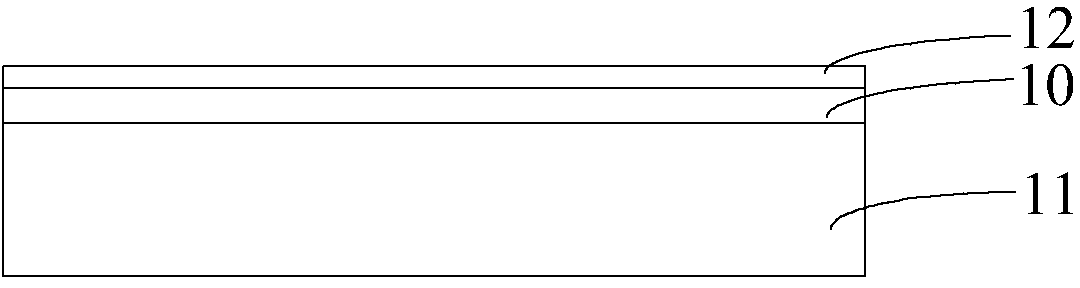

[0041] refer to Figure 1 to Figure 4 , the first method is the glass sheet fixed support method, specifically: refer to figure 1 , providing a wafer 10 with a thickness of 725 microns, on which semiconductor devices (not shown) have been formed, for example, several Insulated Gate Bipolar Transistors (IGBT, Insulated Gate Bipolar Transistor) with a working voltage of 600 volts are formed. ). refer to figure 2 , paste a glass sheet 11 with a thickness of 725-1000 microns on the front surface of the wafer 10 . Next, the wafer 10 is turned over, and the back side of the wafer 10 is thinned by using a chemical mechanical polishing de...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com