SRAM (static random access memory)-oriented anti-SEU (single-event upset) error accumulation controller and method

A controller and memory controller technology, applied in the field of fault tolerance, can solve the problem that SRAM memory cells cannot be refreshed, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] The patent of the present invention will be described in further detail below in conjunction with the accompanying drawings, which is an explanation of the present invention rather than a limitation.

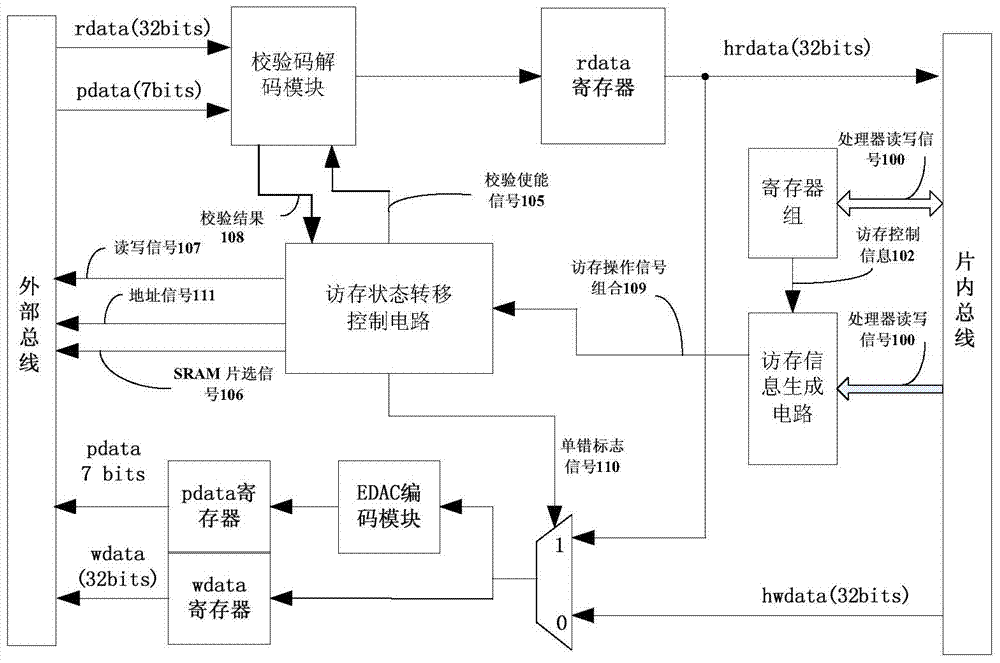

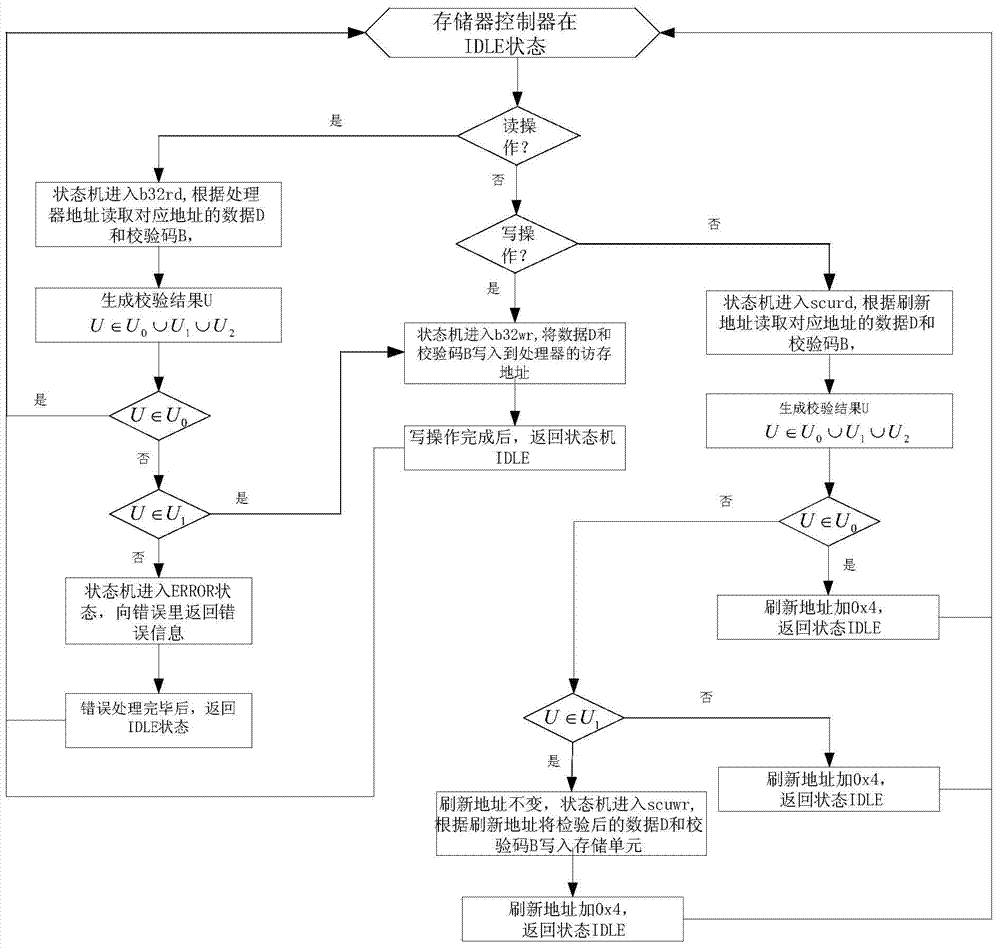

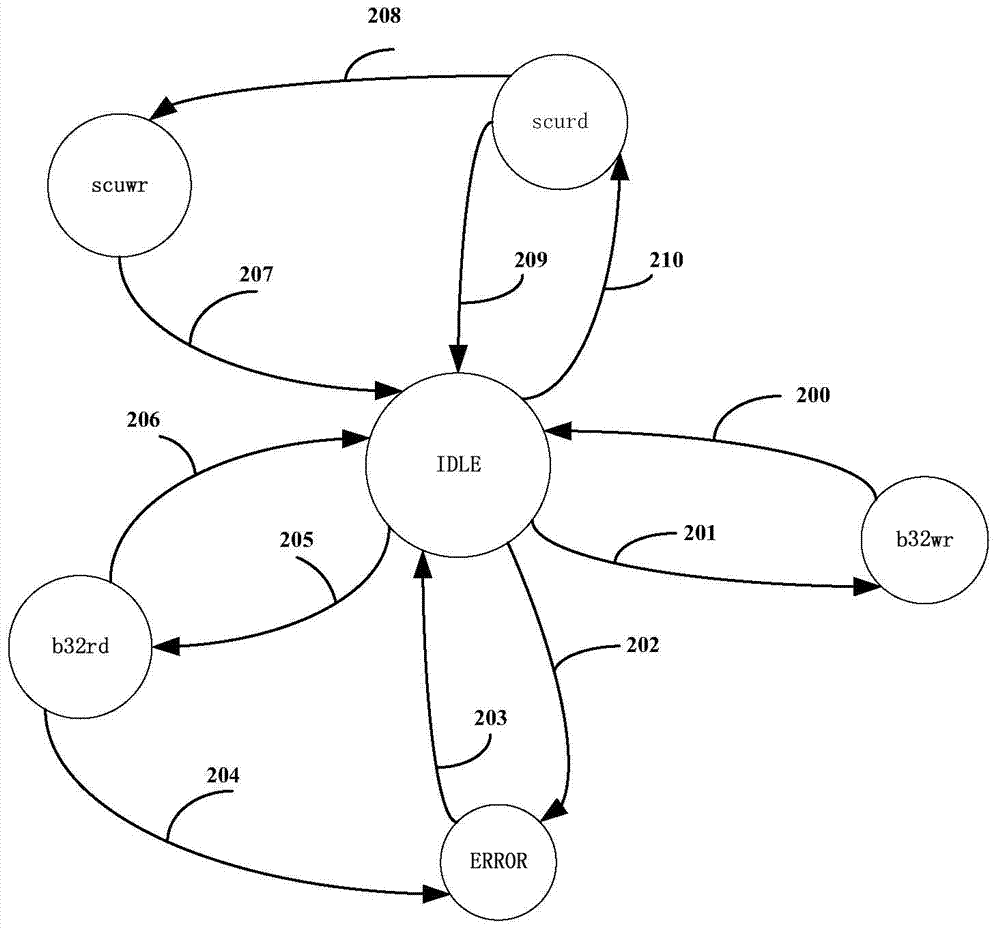

[0051] Such as figure 1 As shown, a SRAM-oriented anti-SEU error accumulation controller, a memory controller that automatically performs refresh actions is set between the on-chip bus and the external bus. When the processor reads the main memory, the microprocessor The memory controller of the memory controller autonomously (that is, without processor intervention) performs a refresh operation of reading→verifying→writing back on the memory unit of the read operation; when the processor performs other operations other than accessing the main memory, the microprocessor The memory controller independently (that is, without processor intervention) performs traversal read → verify → write back operations on all storage units. This method makes full use of the idle time of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com