Method for improving gap filling capability of pre-metal dielectric

A technology of pre-metal dielectric layer and filling capability, which is applied in the manufacturing of electrical components, electric solid-state devices, semiconductor/solid-state devices, etc. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

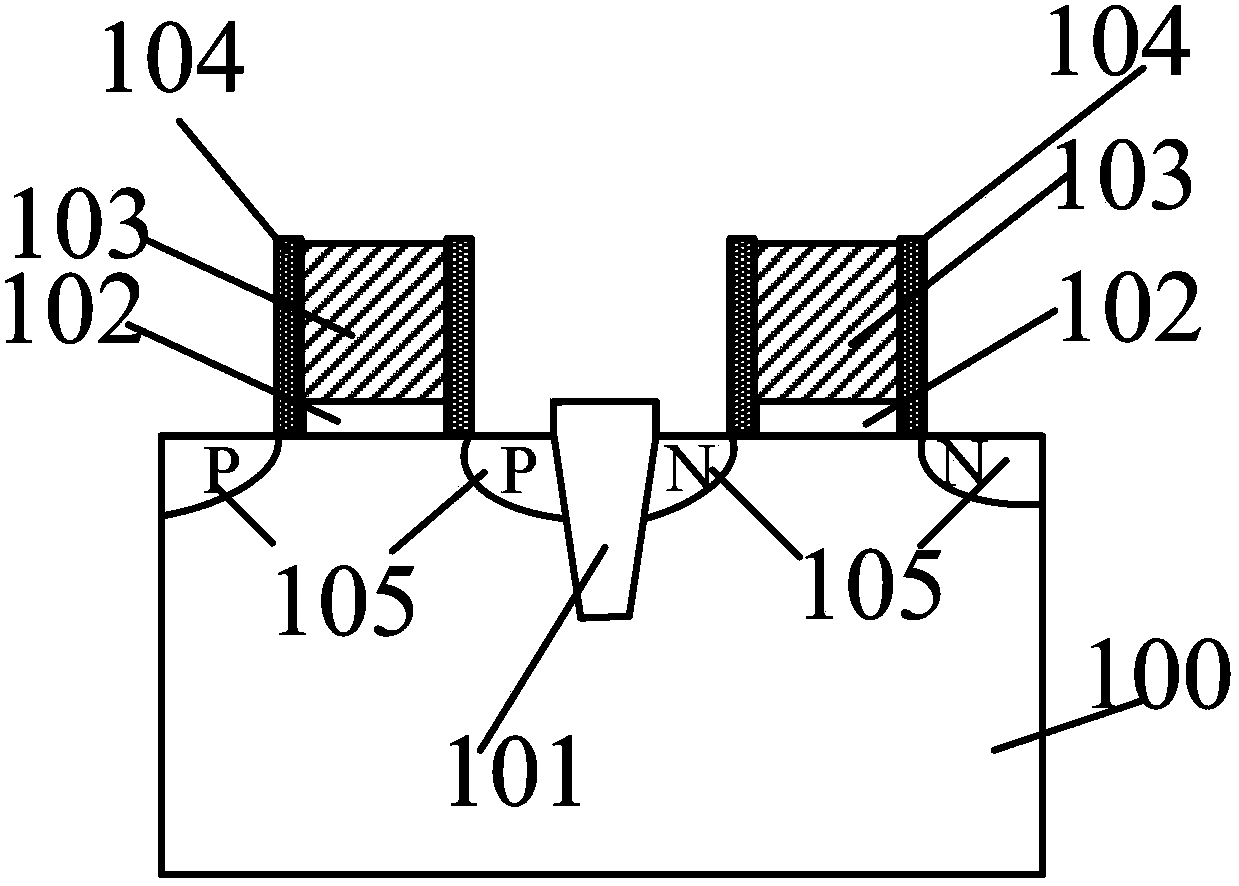

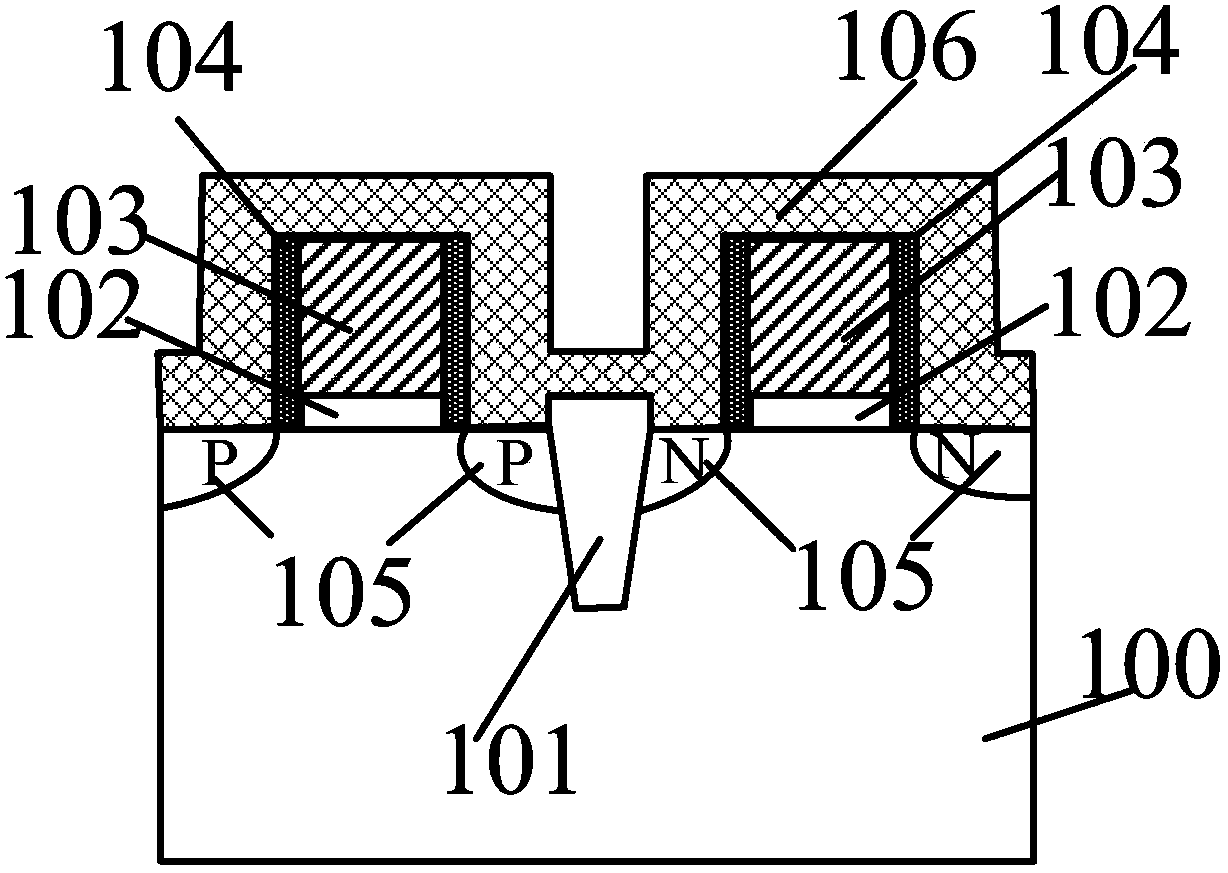

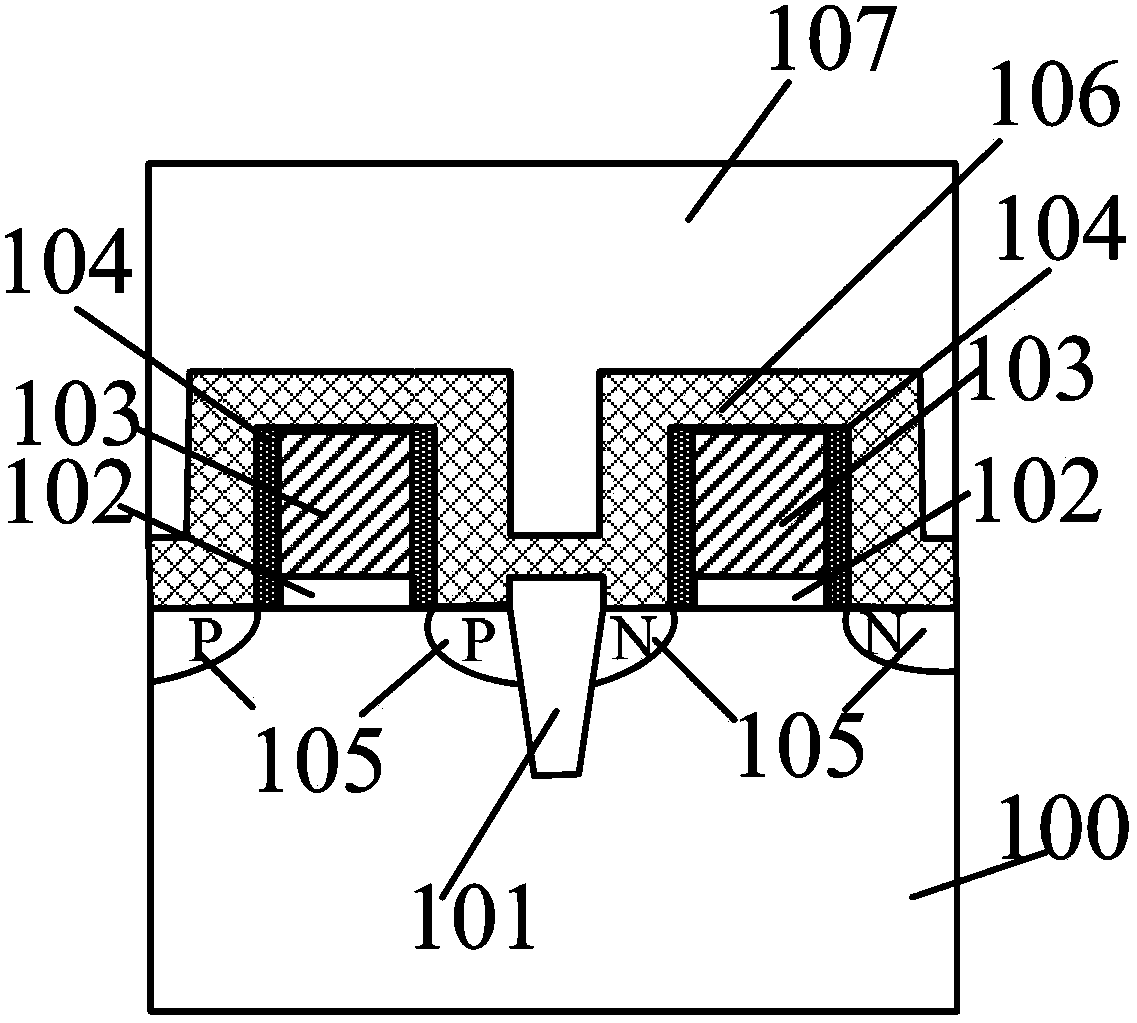

[0025] In order to make the objectives, technical solutions and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings and embodiments.

[0026] Studies have shown that under normal circumstances, the metal pre-metal dielectric layer grows faster on the surface of the silicon oxide layer than on the surface of the stressed silicon nitride layer. However, after the surface of the stressed silicon nitride layer and the surface of the silicon oxide layer are treated with fluorine, the metal front The growth rate of the dielectric layer on the surface of the stressed silicon nitride layer is faster than that on the surface of the silicon oxide layer. Therefore, the present invention uses fluorine treatment to increase the growth selection ratio of the pre-metal dielectric layer on the surface of the stressed silicon nitride layer and the surface of the silicon oxide layer. To achieve the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com