Method for removing noise in level signals

A technology of level signals and glitches, applied in the directions of generating/distributing signals, pulse shaping, etc., can solve the problem of reducing the working speed of the chip, and achieve the effect of less chip area overhead, ensuring correctness, and improving reliability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] Asynchronous analog modules have relatively high requirements for input signals, no glitches, and clean level signals. In combinational logic, because part of the input changes simultaneously in a very short time, the output of the combinational logic has glitches. The asynchronous signal interface is sensitive to glitches and affects the correctness of the function; therefore, it is very important to filter glitches.

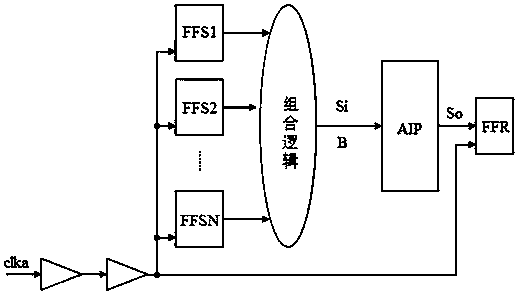

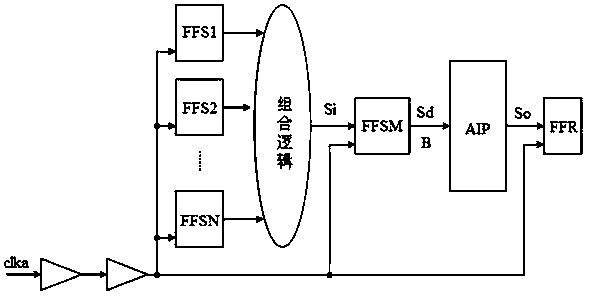

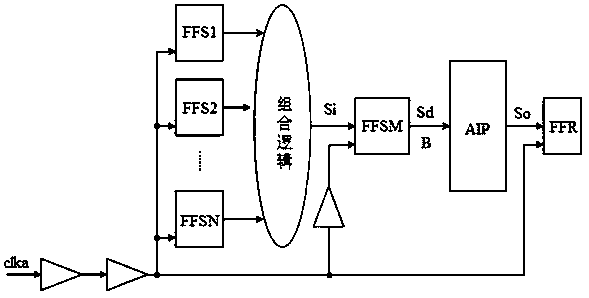

[0015] Such as figure 1 As shown, assuming that there is an input clock domain clka in the design, the output signal Si of the combinational logic is composed of the output signals of several input registers FFS1~FFSN belonging to the combinational logic of the input clock domain clka, and for the asynchronous analog module AIP It is an asynchronous signal. Assume that the input clock domain clka inputs data into the input registers FFS1~FFSN of the combinational logic at the rising edge of the nth clock cycle, and generates the output signal Si of the comb...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com