MOS device, manufacturing method of MOS device and manufacturing method of CMOS devices

A technology of MOS devices and manufacturing methods, which is applied in the manufacture of semiconductor/solid-state devices, semiconductor devices, electrical components, etc., can solve the problems of affecting the switching speed of devices and the inability to accurately control the thickness of metal gates, so as to reduce parasitic capacitance and save production cost, performance-enhancing effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

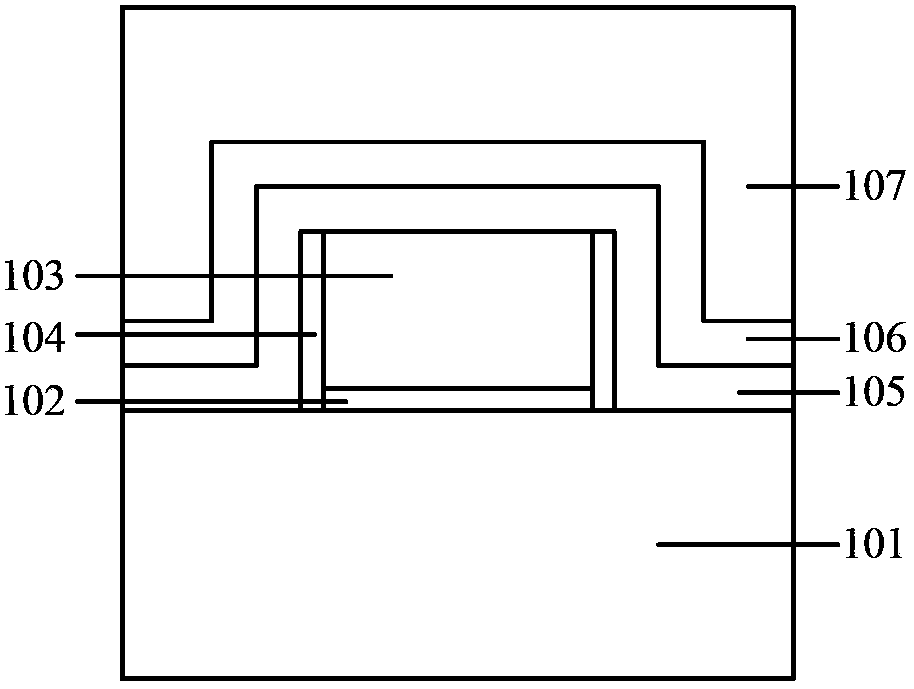

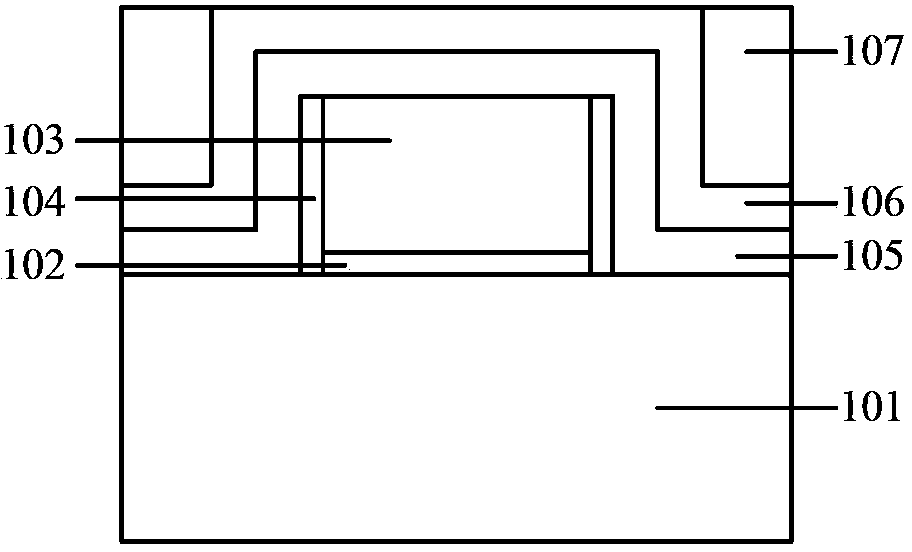

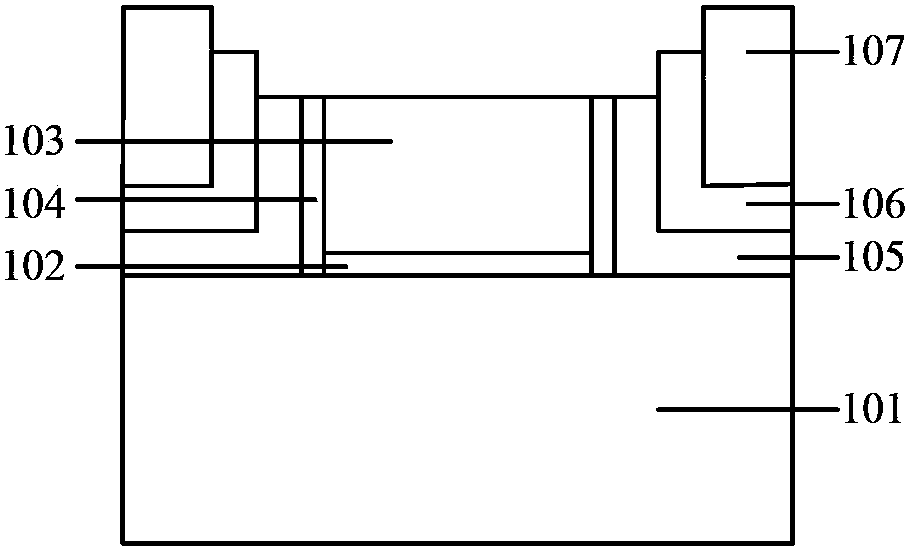

[0060] In order to make the above-mentioned objects, features and advantages of the present invention more obvious and understandable, the specific embodiments of the present invention will be described in detail below with reference to the accompanying drawings.

[0061] In the following description, many specific details are set forth in order to fully understand the present invention, but the present invention can also be implemented in other ways different from those described here, so the present invention is not limited by the specific embodiments disclosed below.

[0062] As mentioned in the background art section, the parasitic capacitance of MOS devices (including CMOS devices) in the prior art is relatively large, and the thickness difference between polysilicon gate and metal gate is relatively large (after multiple etching treatments, the thickness of the metal gate It is about half of the polysilicon gate), resulting in the difficulty of controlling the thickness of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com