A Realization Method of 1588 Clock Synchronization Function

A technology of clock synchronization and implementation method, which is applied in the direction of synchronization devices, digital transmission systems, electrical components, etc., can solve problems such as software delays are not fixed, support has BUG, and cannot be accurately compensated, so as to speed up locking time and accuracy, reduce Development cost, effect of improving forwarding efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

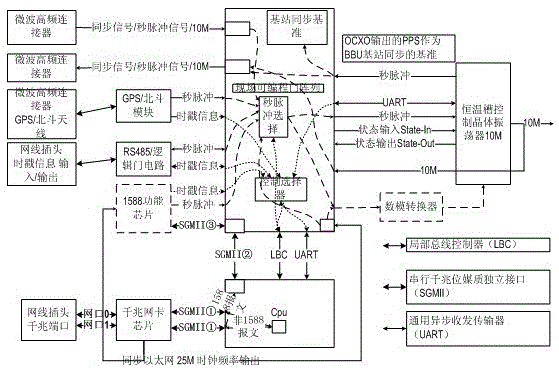

[0178] Combine below figure 1 , figure 2 Typical embodiments of the present invention are further described.

[0179] Such as figure 1 As shown, the hardware required by the present invention includes: PHY chip (BCM54640E), CPU chip (P4080), 1588 function chip (ACS9521), FPGA, and OCXO.

[0180] Such as figure 2 Shown, method flow process of the present invention is as follows:

[0181] 1) The base station equipment is started, and the equipment automatically obtains the external IP provided by the operator. The equipment performs basic settings on the ACS9521, and completes the various mode settings of the 1588 and the internal IP and MAC address settings of the ACS9521.

[0182] 2) BCM54640E accepts network data packets (including 1588 packets) with an upper limit of 2G traffic through network port 0 and network port 1, and sends them to P4080.

[0183] 3) After the P4080 receives the network data packet, it establishes two channels by setting the hardware PCD functio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com