Encapsulating piece for preventing chip salient point from being short-circuited and manufacturing process thereof

A packaging and manufacturing process technology, applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve problems such as voids in plastic packaging materials, reduction of chips and frames, and impact on product reliability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach

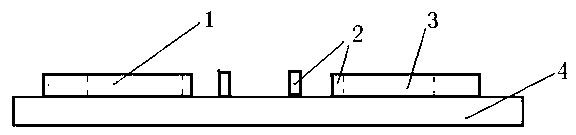

[0028] The specific implementation method is: the copper plate is processed into figure 1 As shown in the frame design, then, the chip bump 5 is dipped in flux, and the chip bump 5 is combined with the copper surface in the corresponding ring-shaped copper pillar 2 through a flip-chip loading machine, and an effective soldering junction is formed under the action of reflow soldering. , the chip bump diameter is 0.2mm, the chip bump height is 0.13mm, and the material is Sn96.5%Ag3.0%Cu0.5%. Finally, the residual flux on the chip bumps 5 is cleaned with plasma water having a resistivity of 1.0 m / Ω.mm or more. The reflux temperature is 260°C, the reflux time is 50~70s, the cleaning temperature is 42°C, the pressure is 40psi, and the cleaning transmission speed is 0.8m / min.

[0029] The function of several materials used: the function of the ring-shaped copper pillar 2 is to prevent the chip bump 5 from collapsing due to melting during the reflow process, causing the chip bump 5...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com