Method for interconnecting and packaging 3-D multi-chip module

A multi-chip module and packaging method technology, applied in the field of microelectronics, can solve problems such as long signal delay time, long interconnection lines, and difficult assembly, so as to improve the speed of operation, reduce size and weight, and reduce volume and weight Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

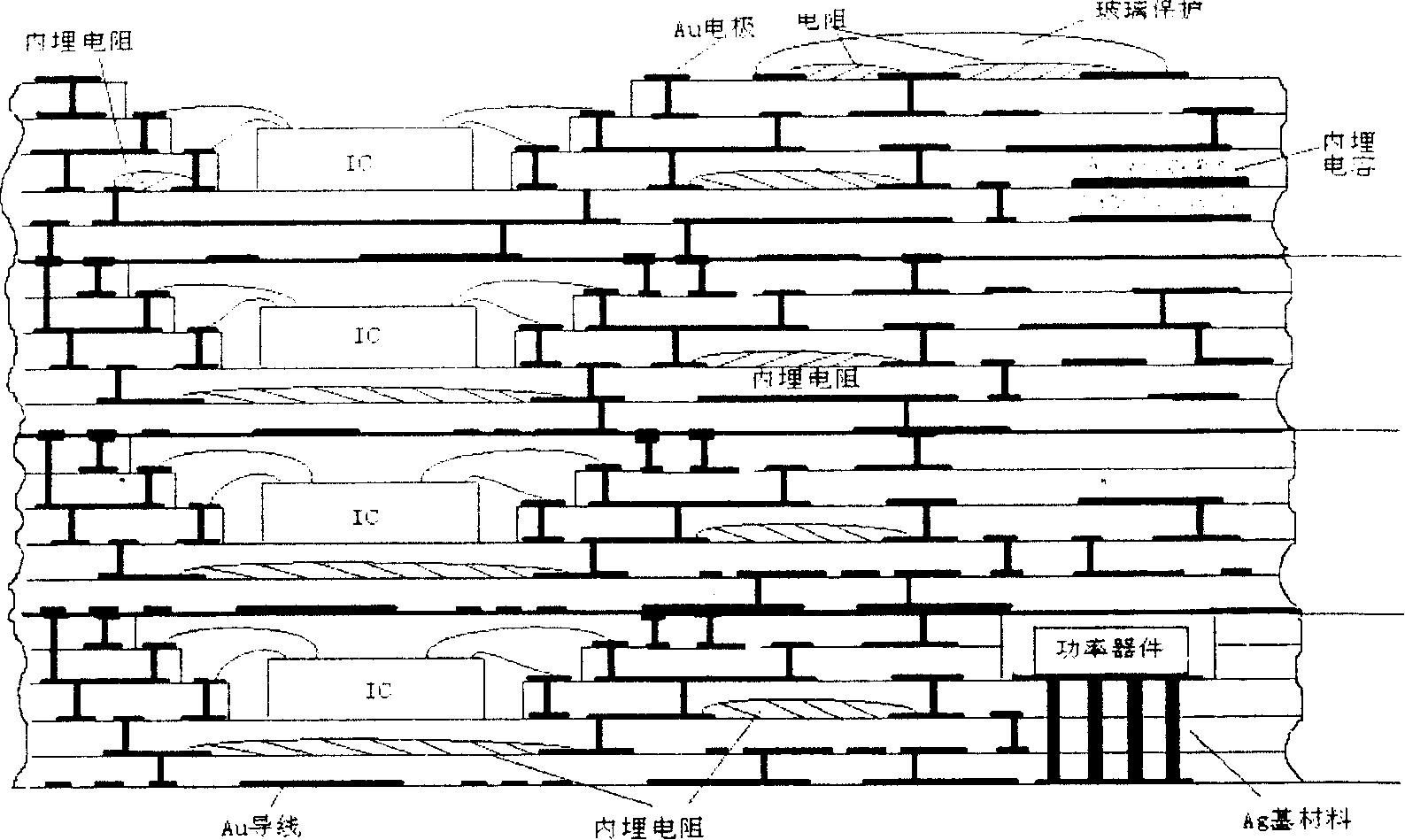

[0045] The 3D-MCM interconnection and packaging method is a key technology in 3D packaging. The three-dimensional multi-chip module interconnection and packaging method of the present invention includes the following content:

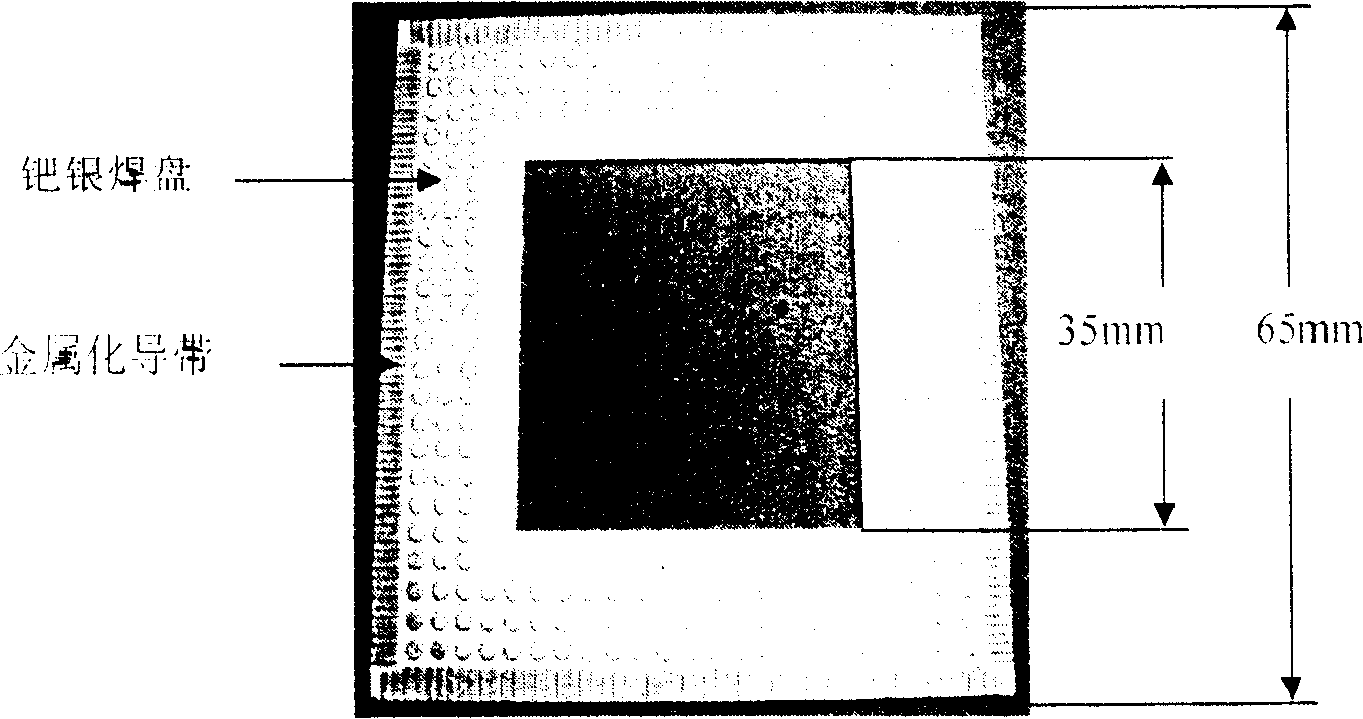

[0046] 1. Design of the back-shaped transition wiring substrate under the laminated module

[0047] By scanning the metallization pattern under the MCM laminated module, the position and size of the metallized pad for vertical interconnection under the MCM laminated module can be accurately measured, avoiding the deformation and size error of the LTCC substrate due to sintering ;According to the above data, the size of the opening in the middle of the back-shaped transition wiring substrate and the specific position of the metallized pad can be clarified; by screen printing the palladium-silver paste, the MCM laminated module will be formed on the inside of the back-shaped transition wiring substrate The metallized interconnection patterns on the bottom...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com