Shielding structure with EBG, 3D packaging structure and preparing method of shielding structure with EBG and 3D packaging structure

A shielding structure, 3D technology, applied in the direction of semiconductor/solid-state device components, semiconductor devices, electrical components, etc., can solve the problems of large vertical size, unfavorable package miniaturization, and long vertical interconnection distance between sensitive chips and interfering chips, etc., to achieve Convenient method, effect of suppressing noise

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

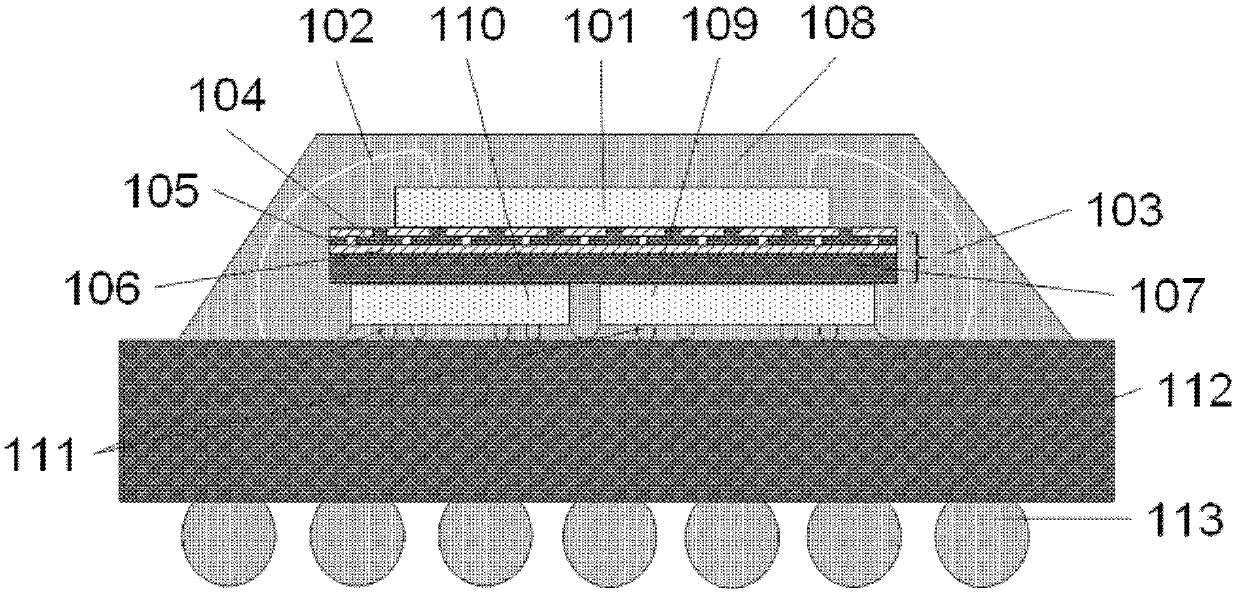

[0026] Such as figure 1 In the shown 3D packaging structure, the bare chips 109 and 110 are bonded on the interconnection substrate 112 by flip-chip bonding, and filled with underfill glue to protect the flip-chip bumps 111 . The individual shielding device 103 with the EBG structure is fixed on the bare chips 109 and 110 with an adhesive. The shielding device 103 includes a support plate 107, a first metal plane 106 etched with a periodic EBG structure, an insulating layer 105, and a second metal plane 104, wherein the unit shape, number and even structural deformation of the periodic EBG structure suppress noise as required Frequency band decision. The support plate can be a variety of substrates such as silicon-based or glass-based, organic substrates, and even ceramic substrates. The insulating material of the corresponding insulating layer 105 may be SiO 2 、Si 3 Ni 4 , organic substrate materials or ceramic materials and other materials. The bare chip 101 is fixed o...

Embodiment 2

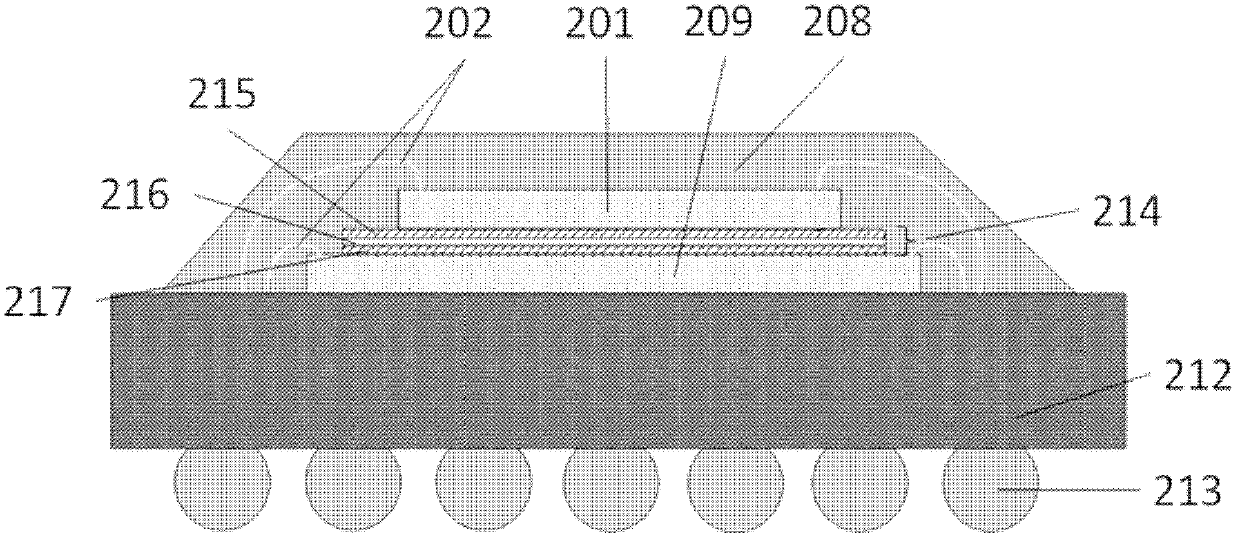

[0037] Such as figure 2 In the shown 3D packaging structure, the bare chip 209 is bonded on the interconnection substrate 212 by wire bonding. A separate shielding device 214 with an EBG structure is fixed on the bare chip 209 with an adhesive, and the shielding device 214 is prepared using a flexible substrate, including a first metal plane 217, an insulating layer 216, and a second metal layer etched with a periodic structure. Plane 215. Among them, the unit shape, quantity and even structural deformation of the periodic structure are determined according to the noise frequency band to be suppressed. The bare chip 201 is fixed on the shielding device 214 with an adhesive, and bonded to the interconnection substrate 212 by wire bonding. The bonding wire 202 is made of various materials such as gold wire, copper wire or aluminum wire. Potting compound 208 such as plastic encapsulant is filled between the 3D stacked bare chips 201 and 209 and the shielding device 214 to fix ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com