Integrated LED (Light Emitted Diode) chip and manufacturing method thereof

A technology for LED chips and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve problems such as difficulty in making clear and tidy graphical interfaces, damage to equipment wafers, and excessive processes. Effective light-emitting area, reduced pitch, and simple production process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

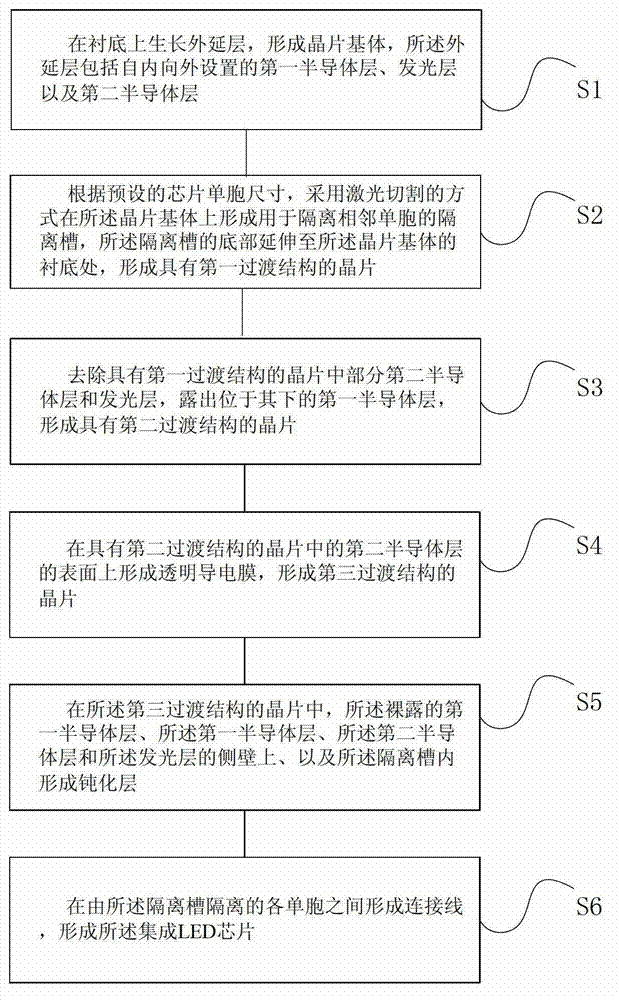

[0044] A method for manufacturing an integrated LED chip, comprising the following steps:

[0045] 1. A sapphire substrate is used, and an epitaxial layer is grown on the substrate material. The epitaxial layer structure includes a buffer layer, an intrinsic semiconductor layer, a first semiconductor layer, a light-emitting layer and a second semiconductor layer from bottom to top.

[0046] 2. Routine cleaning of the epitaxial wafer; a protective layer is formed on the surface by means of evaporation, sputtering, vapor deposition, etc. The material of the protective layer is preferably silicon oxide material, and the thickness is preferably

[0047] 3. Use a laser cutting machine commonly used in the industry to laser cut the wafer according to the preset chip unit cell size. By adjusting the power of the laser to 0.9W and the moving speed of the laser cutting machine relative to the wafer monomer to 45mm / s, the The cutting depth is controlled at 6 μm; the section formed by ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com