Non-volatile memory with P+ floating gate electrode and preparation method thereof

A non-volatile, memory technology, applied in the direction of electrical solid-state devices, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problems of easy loss of written data, influence on reliability, and complexity, so as to improve data storage time and improve The effect of using reliability and reducing the cost of use

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

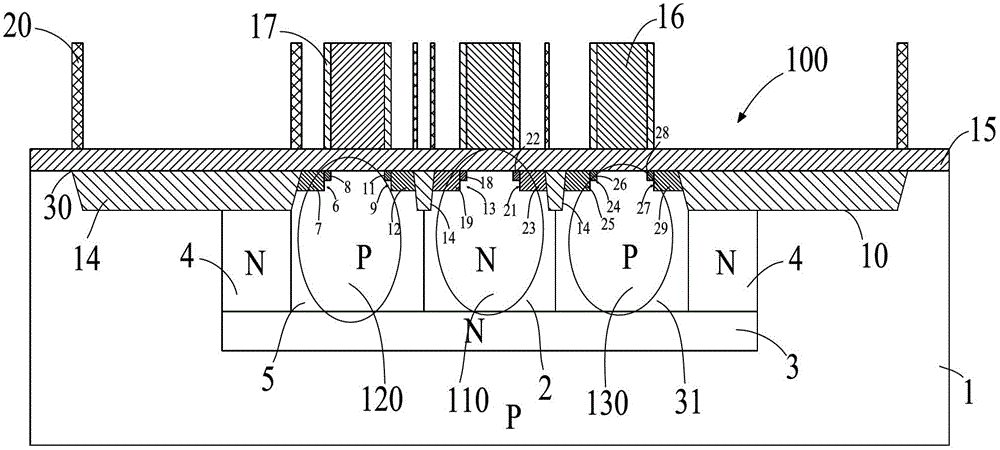

[0068] Such as figure 1 with Figure 13 Shown: In order to make the non-volatile memory compatible with the CMOS logic process and enable the non-volatile memory to store for a longer period of time, the non-volatile memory includes a P conductivity type substrate 1, a P conductivity type substrate 1 The material is silicon. At least one memory cell 100 is provided on the upper part of the P conductivity type substrate 1, and the memory cell 100 includes a PMOS access transistor 110, a control capacitor 120 and a programming capacitor 130, and a gate electrode is deposited on the surface of the P conductivity type substrate 1. The dielectric layer 15 , the gate dielectric layer 15 covers the surface corresponding to the memory cell 100 , and the PMOS access transistor 110 , the control capacitor 120 and the programming capacitor 130 are isolated from each other by the domain dielectric region 14 in the P conductivity type substrate 1 . The domain dielectric region 14 is loca...

Embodiment 2

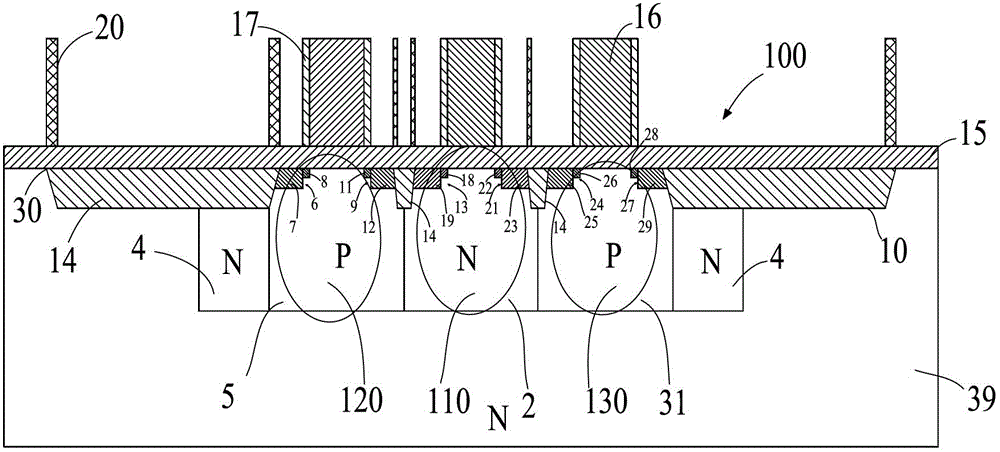

[0099] Such as figure 2 with Figure 25Shown: In this embodiment, the semiconductor substrate is an N-conductive type substrate 39. When the N-conductive type substrate 39 is used, there is no need to form the second N-type region 3 in the N-conductive type substrate 39, that is, the second P-type region 5 and the second P-type region 5. The three P-type regions 31 are in direct contact with the N-type conductivity type substrate 39 , and at the same time, the first N-type region 2 and the third N-type region 4 are also in direct contact with the N-type conductivity type substrate 39 . After adopting the N conductive type substrate 39 , the rest of the structure is the same as that of Embodiment 1.

[0100] Such as Figure 15~Figure 25 Shown: the non-volatile memory of the above structure can be realized through the following process steps, specifically:

[0101] a. An N conductive type substrate 39 is provided, and the N conductive type substrate 39 includes a first main ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com