SRAM (Static random access memory) bit line leakage current compensation circuit

A technology for compensating circuits and leakage currents, applied in information storage, static memory, digital memory information, etc., can solve the problems of SRAM performance degradation and achieve the effect of eliminating adverse effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

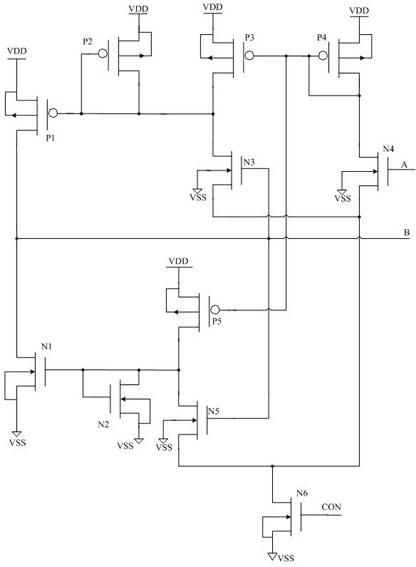

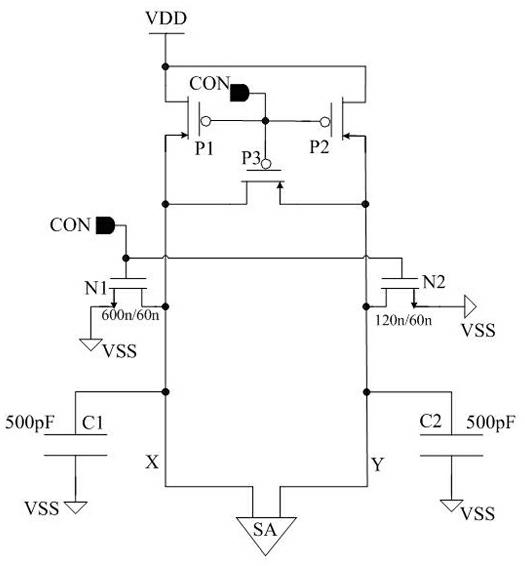

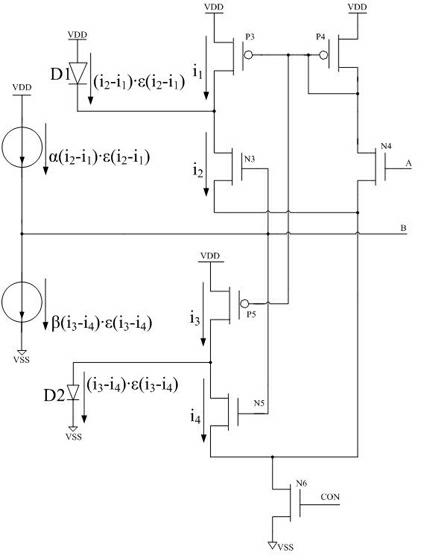

[0014] The SRAM bit line leakage current compensation circuit of the present invention is used as an auxiliary circuit of the SRAM circuit, and two identical compensation circuits are provided to jointly realize the auxiliary compensation of the SRAM circuit (main circuit). Each compensation circuit ( figure 1 ) includes five PMOS transistors P1~P5 and six NMOS transistors N1~N6; the source terminals of the PMOS transistors P1~P5 are respectively connected to their respective body terminals and connected to the power supply voltage VDD, and the body terminals of the NMOS transistors N1~N6 are connected to The power ground VSS, the source end of NMOS transistor N1, the source end of NMOS transistor N2, and the source end of NMOS transistor N6 are all connected to their respective body ends, the drain end of PMOS transistor P1 is connected to the drain end of NMOS transistor N1, and the drain end of PMOS transistor P1 The gate terminal of the PMOS transistor P2, the drain termi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com