Method for forming metal gate

A metal gate and metal layer technology, which is applied in the direction of electrical components, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems of metal gate resistivity change, semiconductor device failure, etc., to improve the sag situation and prevent thickness change Small, the effect of improving electrical performance and reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

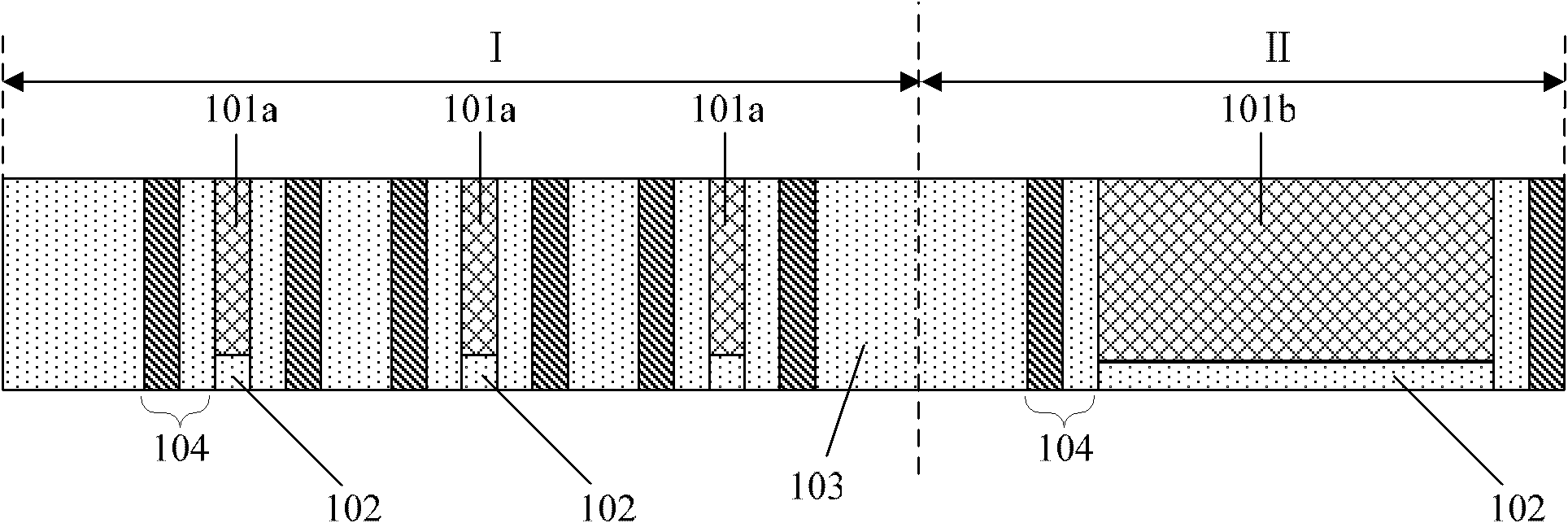

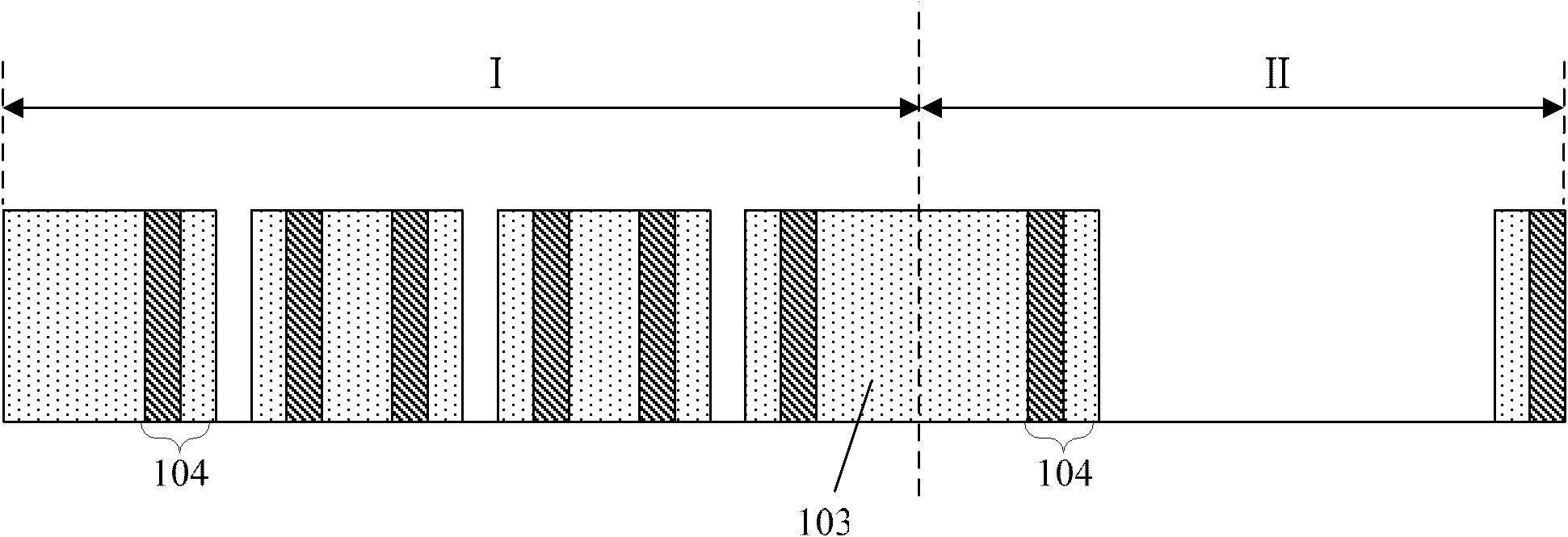

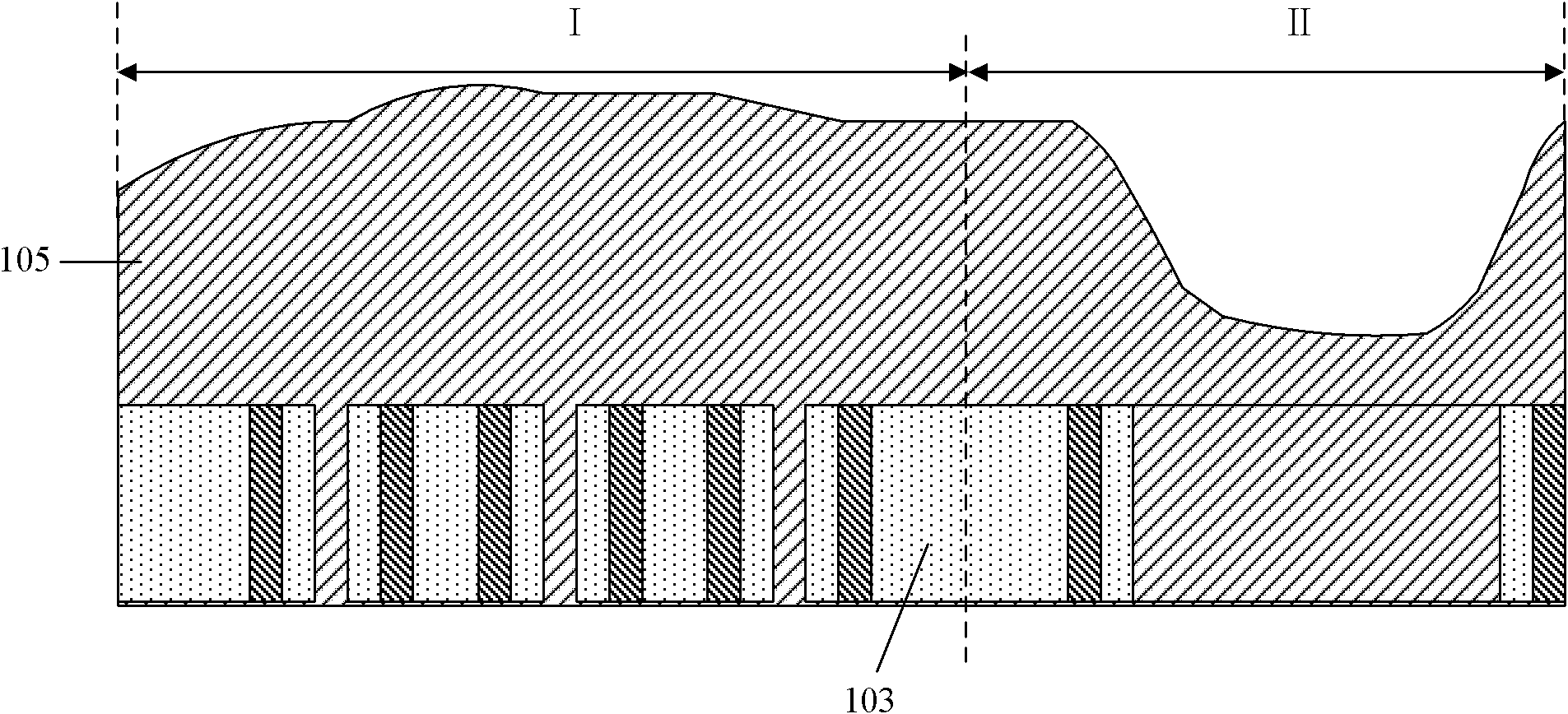

[0039] Figure 6 to Figure 15 It is a schematic cross-sectional view of the first embodiment of the metal gate forming method of the present invention. Such as Figure 6As shown, a semiconductor substrate 200 is provided; the surface area of the semiconductor substrate 200 is divided into a core unit area I and a peripheral circuit area II; a sacrificial oxide layer 202 and a polysilicon gate 201 are sequentially formed on the semiconductor substrate 200 . Among them, in the core cell area I, due to the high device density, there are relatively many polysilicon gates 201a, and the critical dimension of the polysilicon gates 201a is relatively small; in the peripheral circuit area II, due to the low device density, the polysilicon gates 201b is relatively sparse, and the key size is relatively large. The specific process of forming the polysilicon gate 201a, 201b is as follows: form a sacrificial oxide layer 202 on the semiconductor substrate 200 by chemical vapor depositio...

no. 2 example

[0056] Figure 16 to Figure 25 It is a schematic cross-sectional view of the second embodiment of the metal gate forming method of the present invention. Such as Figure 16 As shown, a semiconductor substrate 300 is provided; the surface area of the semiconductor substrate 300 is divided into a core unit area I and a peripheral circuit area II; a sacrificial oxide layer 302 and polysilicon gates 301a, 301b are formed on the semiconductor substrate 300 . Among them, the core cell area I has more polysilicon gates 301a due to the high density of devices, and the critical dimensions of the polysilicon gates 301a are smaller; the peripheral circuit area II has fewer polysilicon gates 301b because of the lower density of devices, and the critical dimensions Also larger. The specific process of forming the polysilicon gates 301a and 301b is as described in the first embodiment.

[0057] Such as Figure 17 As shown, sidewalls 303 are formed on the semiconductor substrate 300 on...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com