Etching method and etching device for mask layer and etching method for interlayer dielectric layer

A technology of interlayer dielectric layer and mask layer, which is applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as time-consuming and cost-consuming, difficulty in exciting radio frequency and biasing radio frequency, etc., to avoid insufficient kinetic energy, Effect of suppressing damage results and low cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

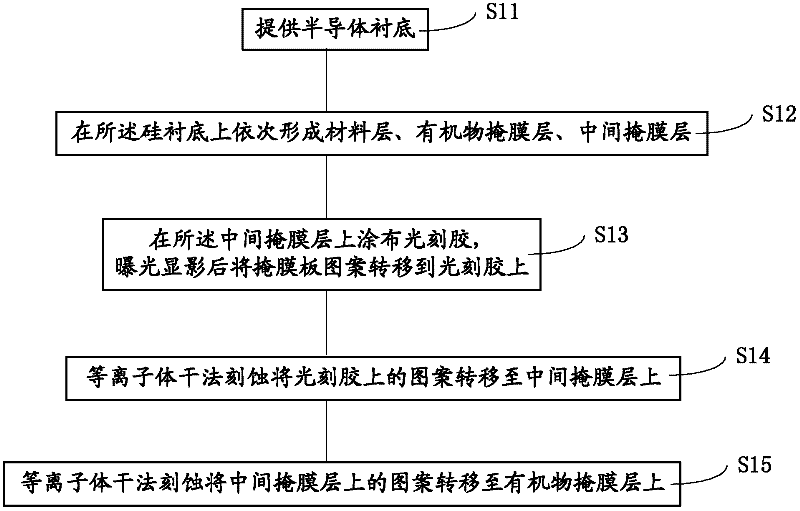

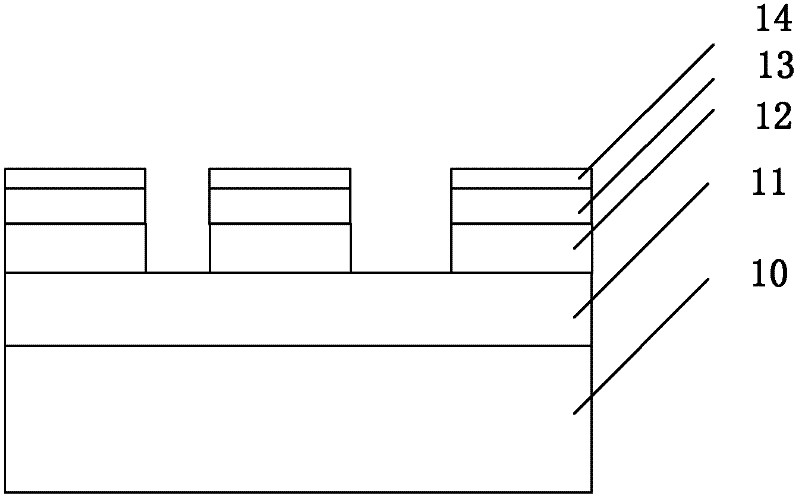

[0047] figure 1 It is a flow chart of the etching method of the mask layer provided in the first embodiment, figure 2 It is a schematic diagram of the final structure after the method is executed. The following combination figure 1 and figure 2 , which details the method.

[0048] First, step S11 is performed to provide a semiconductor substrate; in the first embodiment, the semiconductor substrate is a silicon substrate 10 , and germanium can also be selected as required.

[0049] Next, step S12 is performed to sequentially form a material layer, an organic mask layer, and an intermediate mask layer on the silicon substrate 10 .

[0050] The material layer can be metal, dielectric layer or silicon. In the first embodiment, the interlayer dielectric layer 11 is taken as an example. The material of the interlayer dielectric layer 11 is silicon-containing inorganic material, which can be used to form trenches in subsequent processes. .

[0051] In the first embodiment, t...

Embodiment 2

[0069] The second embodiment provides a method for etching an interlayer dielectric layer, such as Figure 4 As shown, after the steps S11-S15 in the first embodiment are executed, step S16 is then executed to etch the underlying interlayer dielectric layer 11 using the patterned organic mask layer as a mask. In the second embodiment, the organic mask layer follows the amorphous carbon layer 12 of the first embodiment.

[0070] The etching process in this step can use plasma dry etching, and in this process, plasma radio frequency excitation voltage is applied to generate plasma. The frequency range of the plasma excitation radio frequency voltage includes: 20MHz to 120MHz, which can be specifically determined according to the Plasma concentration and distribution requirements to adjust. In addition, this step can also use an existing process.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com