Method for manufacturing double-layer metal-insulator-metal capacitor by using copper damascene process

A double-layer metal and metal capacitor technology, which is applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve problems such as incomplete compatibility, and achieve the effect of improving capacitor performance and increasing capacitor density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment ( 1

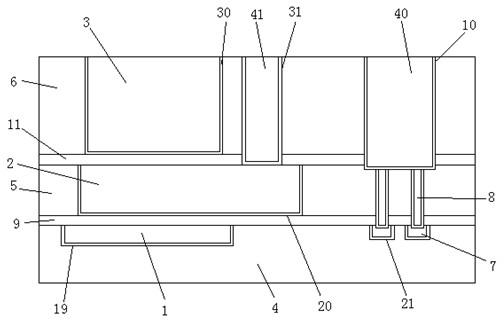

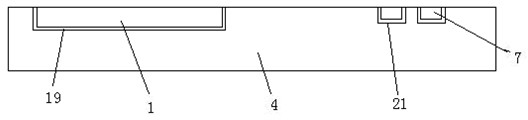

[0035] figure 1 It is a schematic diagram of the structure of a method for manufacturing a double-layer metal-insulating layer-metal capacitor using a copper damascene process in the present invention, as figure 1 As shown, the double-layer metal-insulator-metal (Metal-Insulator-Metal, referred to as MIM) capacitor includes a structure of three layers of metal electrodes and two layers of intermetallic insulating layers, showing the use of copper damascene process in the base dielectric layer 4 Form the first metal electrode groove 19 and the metal interconnection groove 21, and deposit metal in the first metal electrode groove 19 and the metal interconnection groove 21 to make the first metal electrode 1 and the metal interconnection at the same time line 7; deposit the first dielectric barrier layer 9 to cover the base dielectric layer 4, the first metal electrode 1 and the metal interconnection line 7, and then deposit the first dielectric layer 5 to the first dielectric ba...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com