CNT (carbon nano tube)-silicon heterojunction solar cell and manufacturing method thereof

A solar cell and silicon heterojunction technology, applied in circuits, photovoltaic power generation, electrical components, etc., can solve the problem of high processing cost of single crystal silicon, reduce the possibility of recombination, speed up separation, and improve conversion efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

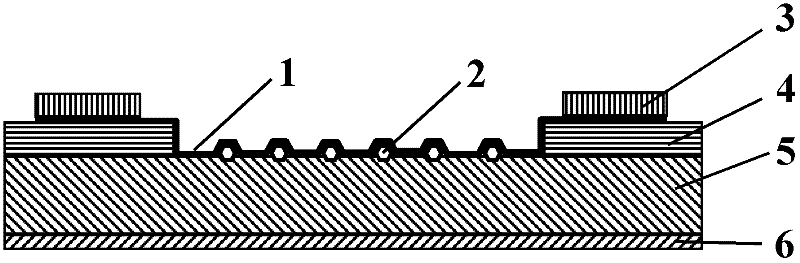

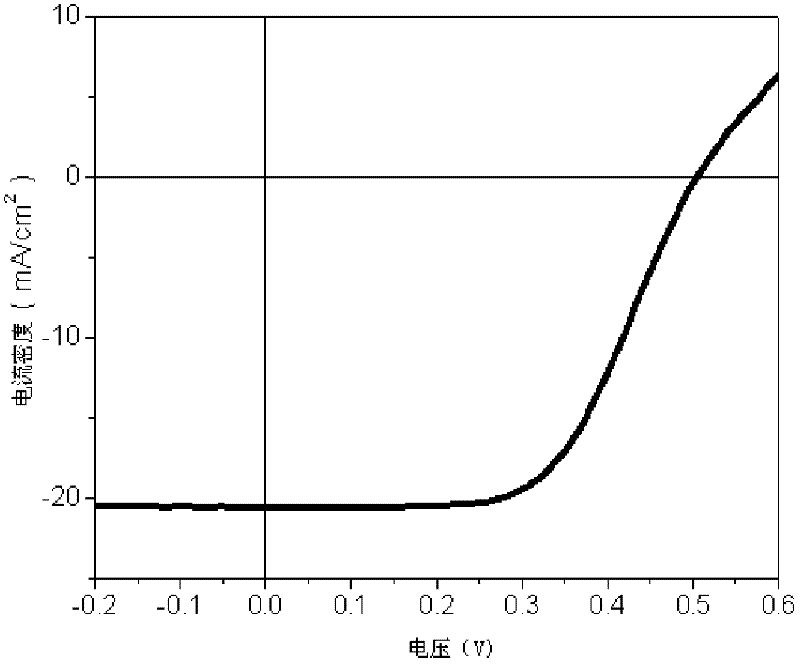

[0027] Embodiment 1, the making of carbon nanotube-silicon heterojunction solar cell

[0028] 1) Prepare SiO with a thickness of 300 nm on the surface of n-type silicon wafer 5 by thermal oxidation 2 thermal oxide layer;

[0029] 2) Using photolithography to etch away the thermal oxide layer on the lower surface of the silicon wafer, and at the same time etch the thermal oxide layer on the central area of the upper surface of the silicon wafer to expose the pure surface of silicon, that is, to obtain a ring-shaped thermal oxide layer covering the upper surface 4 of silicon wafers;

[0030] 3) Evaporate a Ti / Au layer on the lower surface of the silicon wafer to form a good ohmic contact with the lower surface of the silicon wafer as the lower electrode 6, that is, to obtain a Ti / Au layer deposited on the lower surface and a ring-shaped thermal oxide layer deposited on the upper surface Silicon wafer;

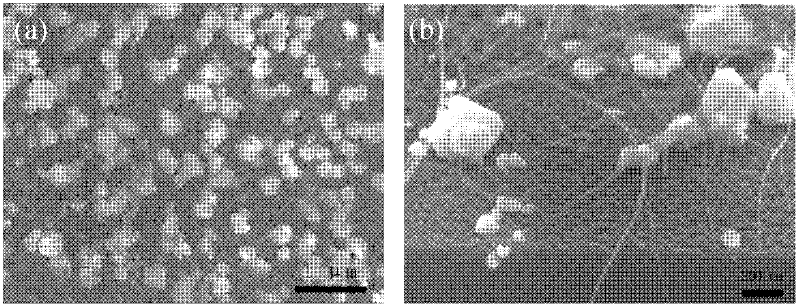

[0031] 4) soak the silicon chip obtained in step 3) in Cu(NO 3 ) 2 Mi...

Embodiment 2

[0035] Embodiment 2, the making of carbon nanotube-silicon heterojunction solar cell

[0036] 1) Prepare SiO with a thickness of 200nm on the surface of n-type silicon wafer by thermal oxidation 2 thermal oxide layer;

[0037] 2) Using photolithography to etch away the thermal oxide layer on the lower surface of the silicon wafer, and at the same time etch the thermal oxide layer on the central area of the upper surface of the silicon wafer to expose the pure surface of silicon, that is, to obtain the upper surface covered with a ring-shaped thermal oxide layer. Silicon wafer;

[0038] 3) Evaporate a Ti / Au layer on the lower surface of the silicon wafer to form a good ohmic contact with the silicon wafer surface as the lower electrode, that is, to obtain a silicon wafer with a Ti / Au layer deposited on the lower surface and a ring-shaped thermal oxide layer deposited on the upper surface ;

[0039] 4) soak the silicon chip obtained in step 3) in Cu(NO 3 ) 2 Mixed aqueous...

Embodiment 3

[0043] Embodiment 3, the making of carbon nanotube-silicon heterojunction solar cell

[0044] 1) Prepare SiO with a thickness of 200nm on the surface of n-type silicon wafer by thermal oxidation 2 thermal oxide layer;

[0045] 2) Using photolithography to etch away the thermal oxide layer on the lower surface of the silicon wafer, and at the same time etch the thermal oxide layer on the central area of the upper surface of the silicon wafer to expose the pure surface of silicon, that is, to obtain the upper surface covered with a ring-shaped thermal oxide layer. Silicon wafer;

[0046] 3) Evaporate a Ti / Au layer on the lower surface of the silicon wafer to form a good ohmic contact with the silicon wafer surface as the lower electrode, that is, to obtain a silicon wafer with a Ti / Au layer deposited on the lower surface and a ring-shaped thermal oxide layer deposited on the upper surface ;

[0047] 4) soak the silicon chip obtained in step 3) in Cu(NO 3 ) 2 Mixed aqueous...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Particle size | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com