Method for manufacturing bottom gate metal oxide thin film transistor

A technology of oxide thin films and transistors, applied in the direction of transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., to reduce stress concentration, improve production pass rate, and solve the effects of easy fracture

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0030] Such as Figure 4 As shown, the manufacturing process of the bottom gate metal oxide thin film transistor of the present invention comprises the following steps:

[0031] a) Deposit a layer of gate electrode film on the glass substrate and form the desired pattern through processes such as photolithography and etching (such as Figure 4 (a) shown).

[0032] b) Deposit a layer of gate insulating layer material (such as Figure 4 (b) shown).

[0033] c) Deposit a layer of metal oxide material to make it an insulator by controlling the process conditions (such as Figure 4 (c) shown).

[0034] d) Apply photoresist 710 and use chemical mechanical polishing (CMP) technology to planarize the photoresist, so that other areas except the vicinity of the channel area are covered by photoresist (as shown in 4(d)) .

[0035] e) Treating the exposed oxide film to transform it into a semiconductor characteristic by adopting vacuum annealing method 810 (as shown in 4(e)).

[00...

Embodiment 2

[0046] Such as Figure 5 As shown, the process flow of this embodiment is similar to that of embodiment 1. The difference is in Figure 5 In (e), the method (820) of annealing treatment in a reducing atmosphere is adopted to realize the transformation of the metal oxide from an insulator to a semiconductor.

[0047] In the process step 820, the sample is heated to 300° C. under a reducing atmosphere such as hydrogen or nitrogen, kept for 30 minutes, and then cooled in air. Increase the carrier concentration of the treated metal oxide film to 10 13 ~10 15 cm -3 In the range, it exhibits semiconducting properties.

Embodiment 3

[0049] Such as Figure 6 As shown, the process flow of this embodiment is similar to that of Embodiment 1. The difference is in Figure 6 In (e), the plasma treatment method (830) is used to realize the transformation of the metal oxide from an insulator to a semiconductor.

[0050] In the process step 830, the sample is placed in a vacuum chamber, and the surface of the sample is treated with argon plasma for 3-5 minutes, and the discharge power is 150W. Increase the carrier concentration of the treated metal oxide film to 10 13 ~10 15 cm -3 In the range, it exhibits semiconducting properties.

[0051] By adopting the process flow in the above-mentioned embodiments 1-3, the process steps of photolithography and etching of the active layer are saved, and chemical mechanical polishing and annealing (or plasma treatment) processes are used instead, which is more efficient. figure 2 The traditional process shown is simple.

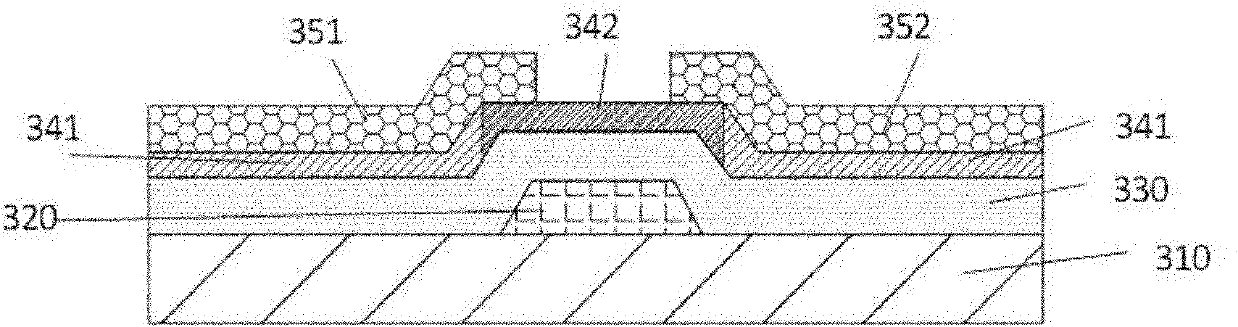

[0052] image 3 It is a schematic structural d...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com