Preparation method of diode chip on P+ substrate and structure of diode chip

A diode and substrate technology, applied in the field of low-voltage diode chips and its manufacturing, can solve the problems of large leakage of low-voltage diodes and poor voltage uniformity in the chip, and achieve the effect of avoiding lateral breakdown and ensuring voltage uniformity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach

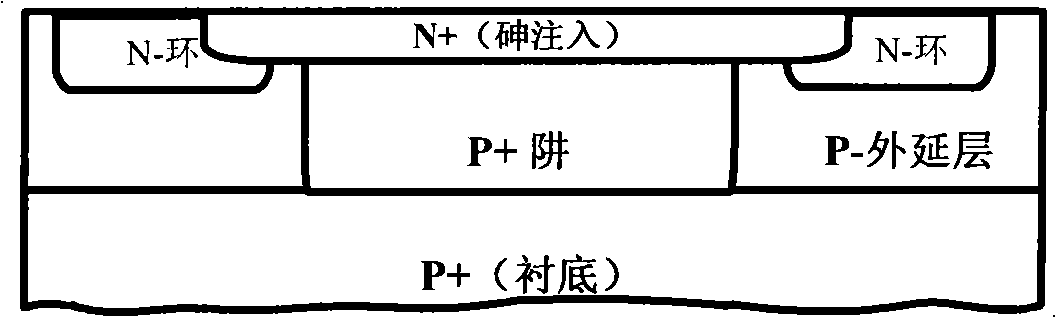

[0030] Below in conjunction with accompanying drawing, the present invention is further described, especially with figure 2 For example, the specific implementation method is as follows:

[0031] A kind of method that the present invention proposes prepares low-voltage diode chip on P+ substrate comprises the steps:

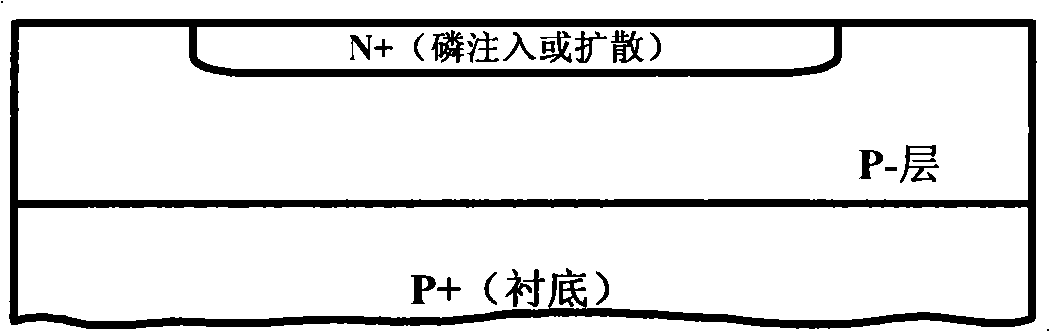

[0032] Step 1: The resistivity of the P+ substrate is about 0.005≤ρ≤0.008Ω.cm, and a P- epitaxial layer with a thickness of 3.0-10.0um and a resistivity of 1.0-5.0Ω.cm is chemically vapor grown at 1050°C.

[0033] Step 2: Form an active region by photolithography and etching on the P- epitaxial layer, and then inject boron into the active region to form a P+ well. The dose of the P+ well depends on the breakdown voltage (for low-voltage diodes below 5.1V , the dose is about 1E15-8E15).

[0034] Step 3: P well annealing temperature is 1100°C-1200°C for 1h-2h.

[0035] Step 4: Form the N-ring region by photolithography and etching, and the N-ring dose is relati...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical resistivity | aaaaa | aaaaa |

| electrical resistivity | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com