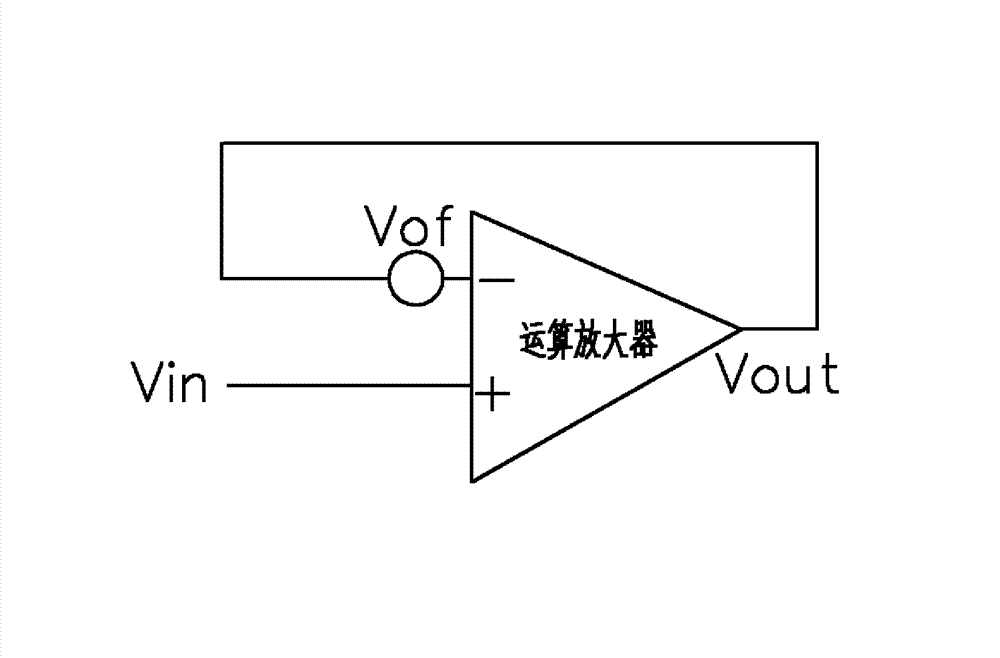

Method and structure for eliminating offset voltage of operational amplifier by using lining bias effect

A technology of bias effect and offset voltage, applied in improving amplifiers to reduce temperature/power supply voltage changes, differential amplifiers, DC-coupled DC amplifiers, etc., can solve problems such as increasing parasitic capacitance, reducing circuit speed, and unable to eradicate offset voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

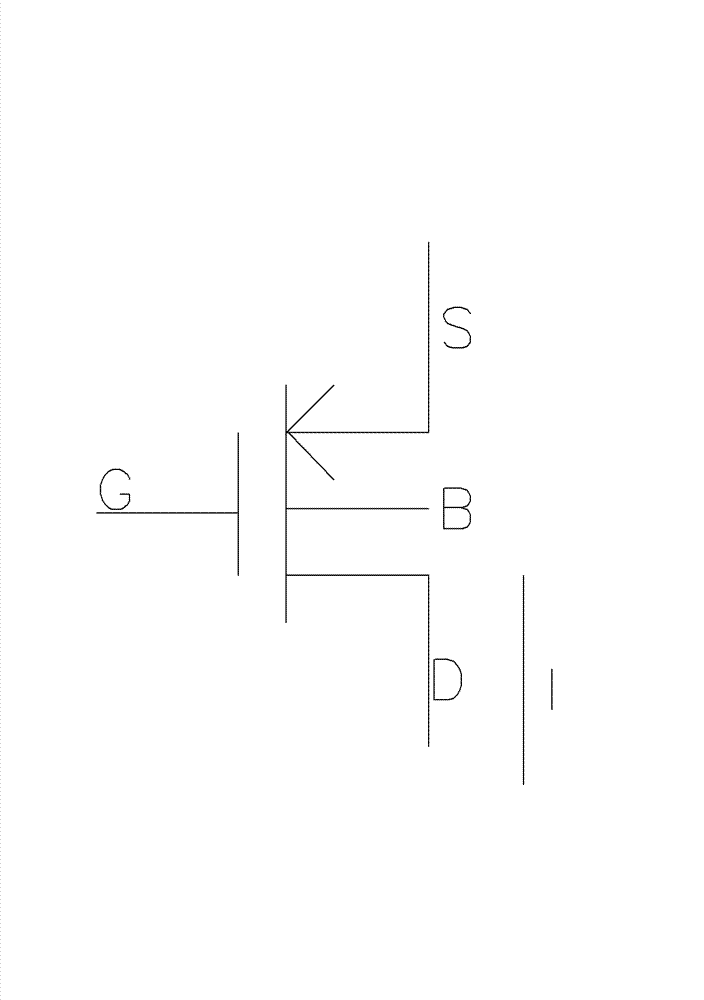

[0025] A method of eliminating the offset voltage of an op amp by using the substrate bias effect, see Figure 4 , Figure 5 , which includes an operational amplifier. When correcting, the two input terminals of the operational amplifier are grounded. Among the two PMOS transistors of the operational amplifier, the substrate voltage of one PMOS transistor is connected to the fixed voltage Vc, and the substrate voltage of the other PMOS transistor can be connected to Variable voltage Vcb, the output terminal Vout of the operational amplifier is connected to the negative pole of the comparator, the positive pole of the comparator is connected to the reference voltage V, and the output of the comparator is connected to the subtractor. In a single clock cycle T, the positive pole of the comparator is smaller than the negative pole. The output is 0, the subtractor subtracts 1, and the value corresponding to the output of the subtractor controls the value of the variable voltage Vcb...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com