FPGA (Field Programmable Gate Array)-based bonded phase frequency doubling method and device

A key phase and frequency doubling technology, applied in the direction of logic circuits using basic logic circuit components, logic circuits using specific components, electrical components, etc. It can improve the stability and reliability, reduce the circuit consumption area, and make the modification flexible and convenient.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

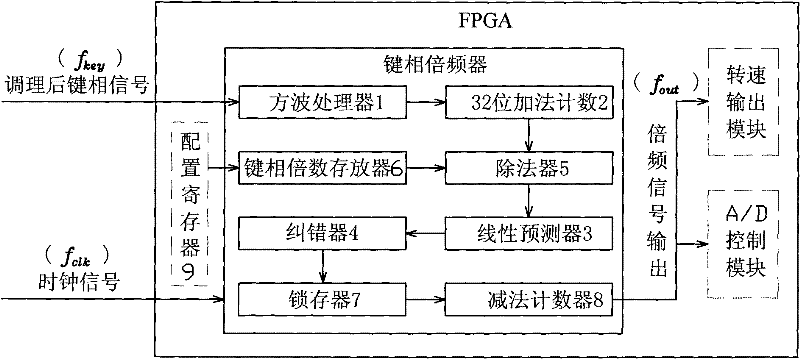

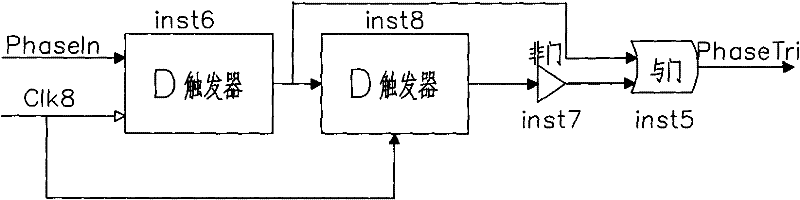

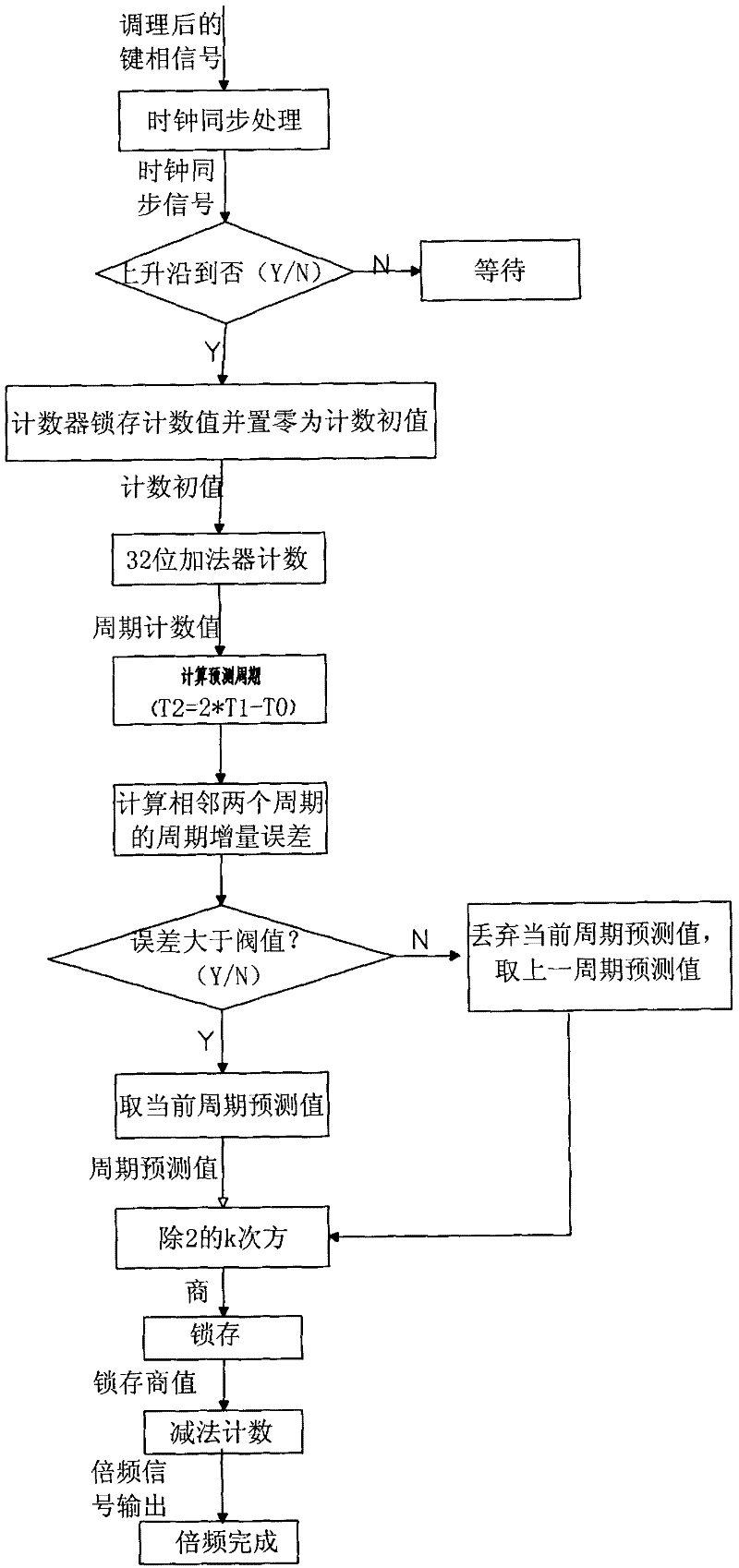

[0025] Such as figure 1 As shown, the FPGA-based key phase frequency multiplier of this embodiment includes a square wave processor 1, an addition counter 2, a linear predictor 3, an error corrector 4, a divider 5, a key phase multiple register 6, a latch Device 7 and subtraction counter 8, described square wave processor 1, addition counter 2, linear predictor 3, error corrector 4, divider 5, key phase multiple register 6, latch 7 and subtraction counter 8 use hardware The description language VHDL is programmed and integrated into an FPGA. The key-phase frequency multiplier is a module in the FPGA device, which accepts the frequency f key The key phase square wave signal, the clock signal and the data in the FPGA configuration register, wherein the key phase multiple 2 is placed in the FPGA configuration register 9 k (k is a positive integer) data, the device output frequency is 2 k f key The frequency multiplied square wave signal; the output multiplied signal can be us...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com