2T embedded FLOTOX EEPROM

A read-only memory and embedded technology, applied in the direction of read-only memory, static memory, information storage, etc., can solve the problems of increasing the difficulty of the process, increasing the difficulty and cost of the process, increasing the complexity of the circuit, and the circuit layout area, etc., to achieve saving Die area effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

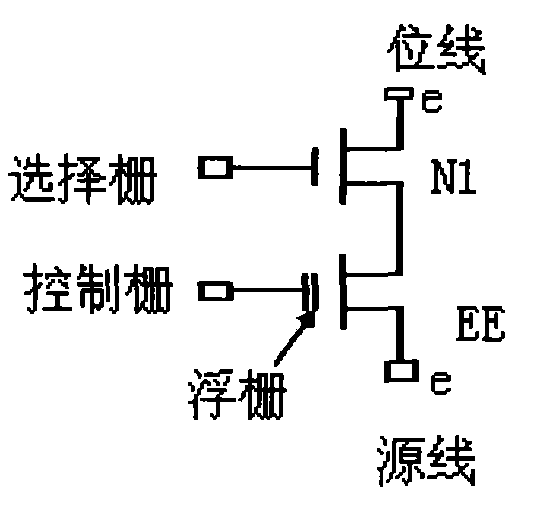

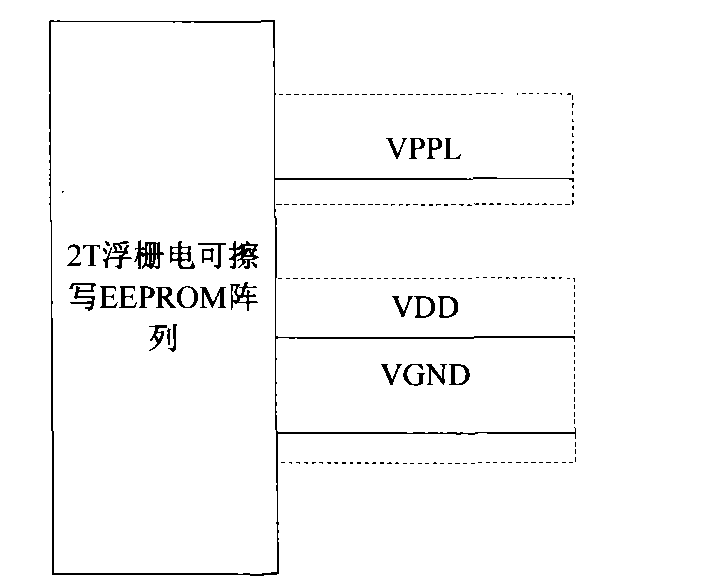

[0016] like figure 2 As shown, the drain terminal of the storage transistor EE is connected as the bit line (Bitline) of the entire memory array, and the source terminal of the selection transistor N1 is used as the source line (Sourceline) of the entire memory array. Its operating voltage is shown in Table 2. When it is necessary to implement a write operation on the memory, a high voltage (VPPL) is applied to the bit line, and 0V is applied to the control gate (control gate) of the storage tube EE, so that The thin oxide layer of the storage tube occurs tunneling (tunneling), pulling electrons out of the floating gate (Floating gate), so that the storage tube is in the "1" state, and the power supply voltage is applied to the selection tube to ensure that it is turned on, and the source line is empty. (floating).

[0017] Table 2:

[0018]

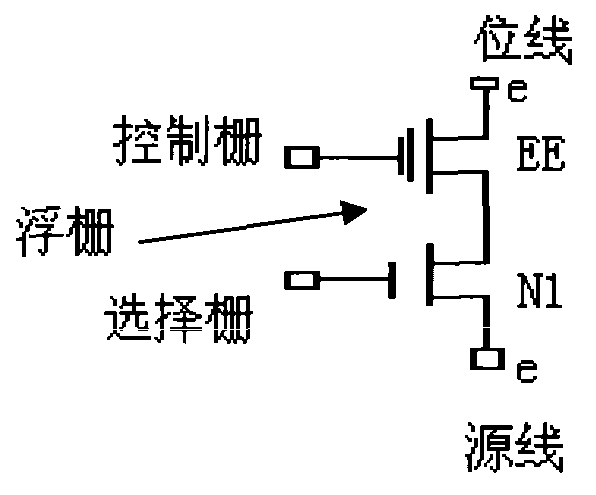

[0019] To realize the erasing (erase) operation, apply high voltage to the control gate, add 0V to the bit line, and inject elect...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com