Structure for implementing DFT of 32-channel parallel data

A data and system realization technology, applied in high-speed digital demodulator, high-speed digital processing, and modulator fields, can solve the problem that analog processing methods cannot achieve variable speed, serial digital demodulation cannot be realized, and sampling clock cannot be directly sent to FPGA, etc. question

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

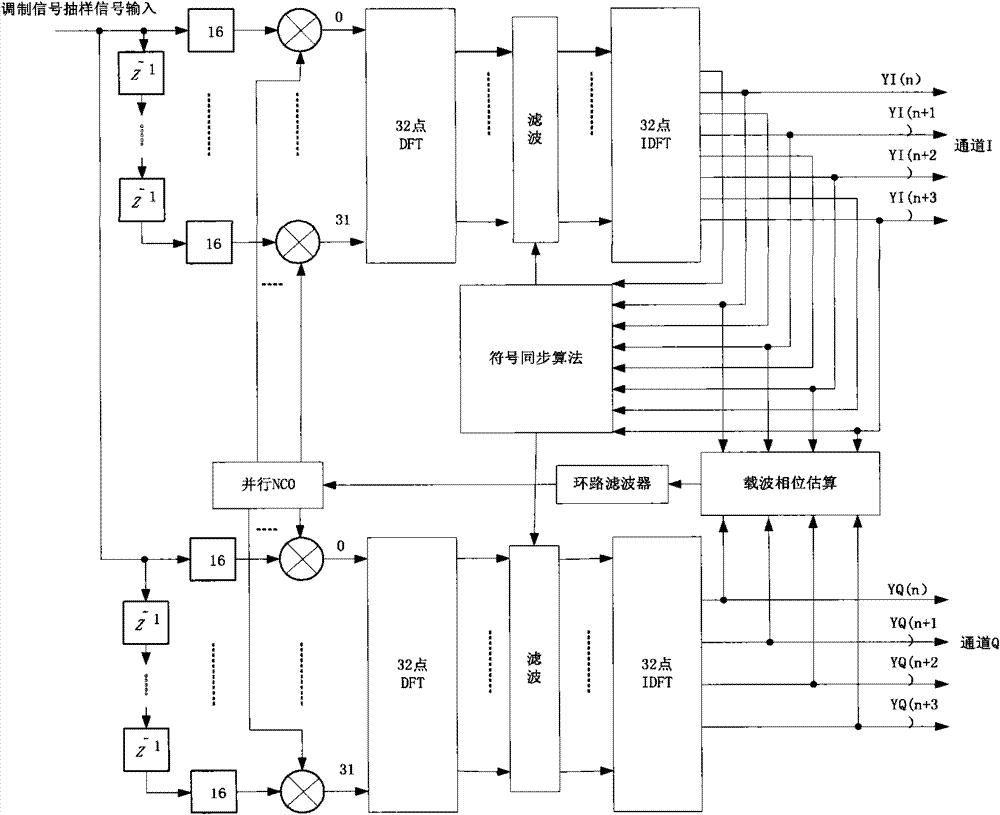

[0032] figure 1 For the specific application method of high bit rate QPSK digital demodulation DFT / IDFT, the digital demodulator uses high-speed AD sampling, the data sent by AD is extracted by 16 times, overlapped and transformed into 32 channels of data, and 32 channels of data are processed after digital down-conversion DFT calculation, then filtering in the frequency domain, IDFT output after filtering, and then parallel clock recovery and carrier recovery to complete data demodulation. After the data is extracted by 16 times, the internal data processing speed is only 1 / 16 of the input, and the internal data processing of the high code rate QPSK demodulator is only 1 / 16 of the sampling clock, so it is very suitable for ultra-high code rate demodulation.

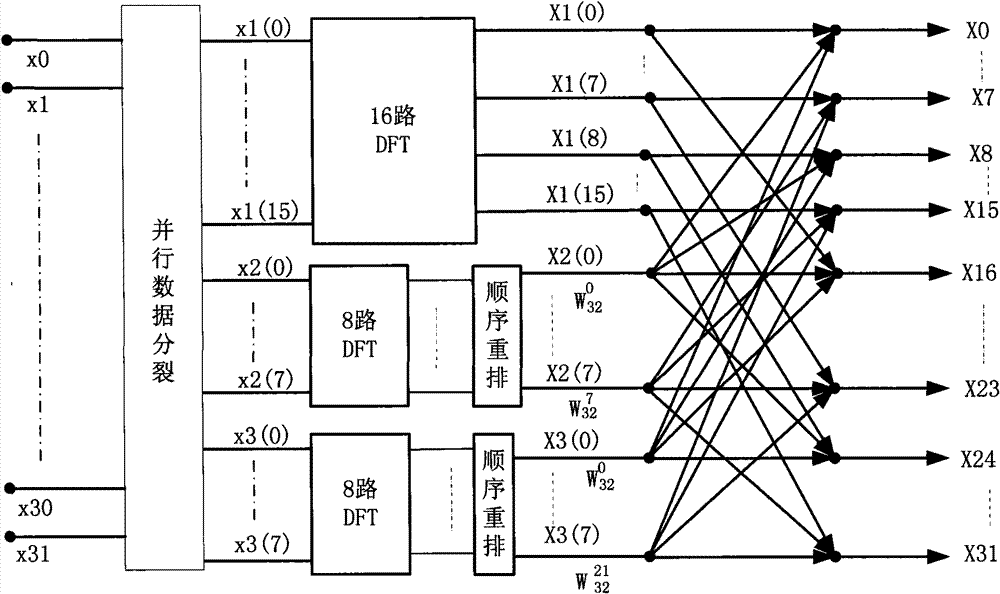

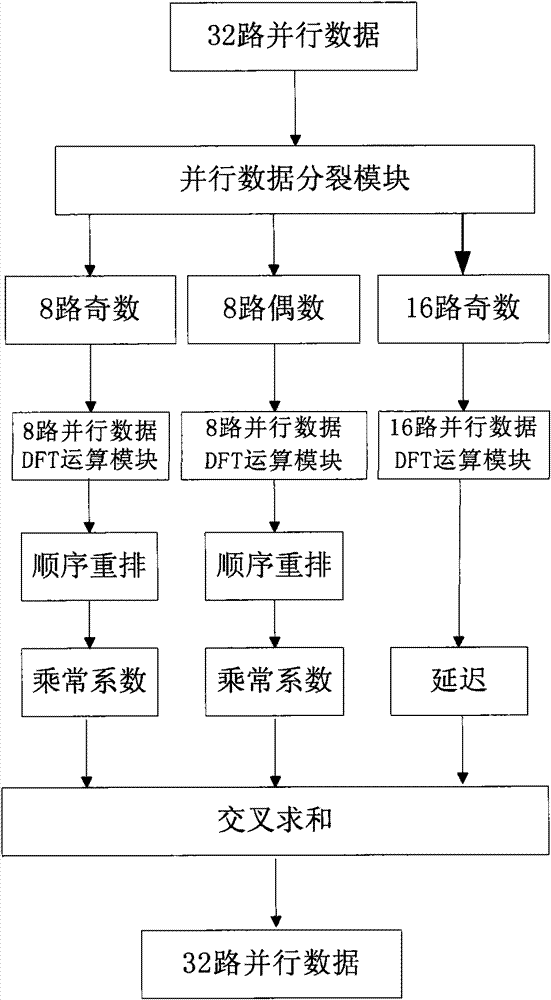

[0033] Since IDFT is the inverse transform of DFT, the embodiment of the p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com