Process for manufacturing surface channel PMOS device with polycide

A technology of surface trenches and manufacturing processes, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as low leakage current, achieve low leakage, simple process, and reduce device size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

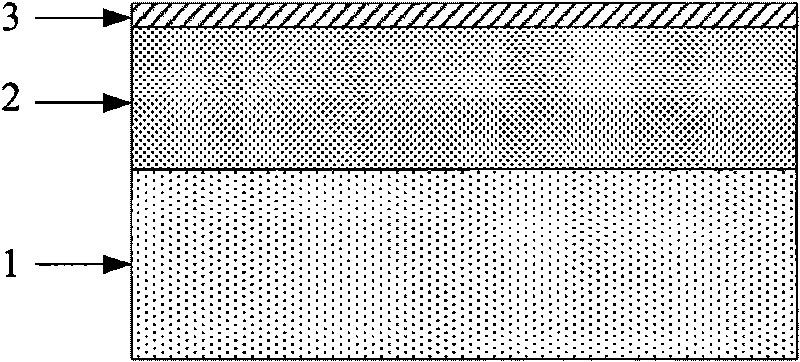

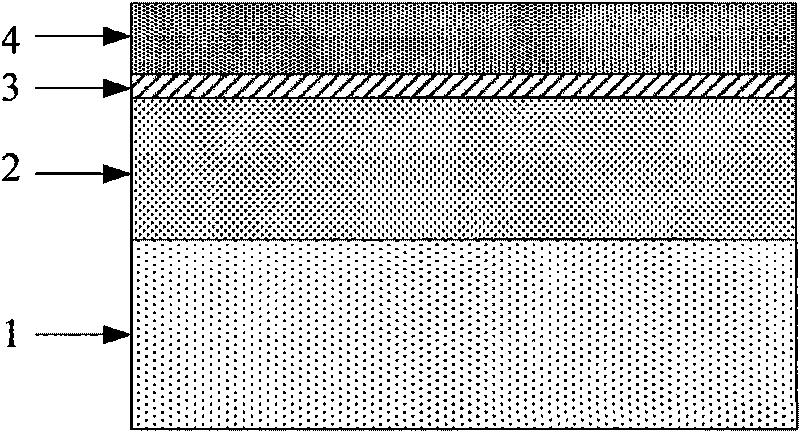

[0017] The fabrication process of the surface channel PMOS device with polysilicon in the present invention usually has a field oxygen isolation, LOCOS isolation or shallow trench isolation (STI) process before the process starts, which is used to isolate the active regions on the silicon wafer from each other. On this basis, the present invention also comprises the following steps:

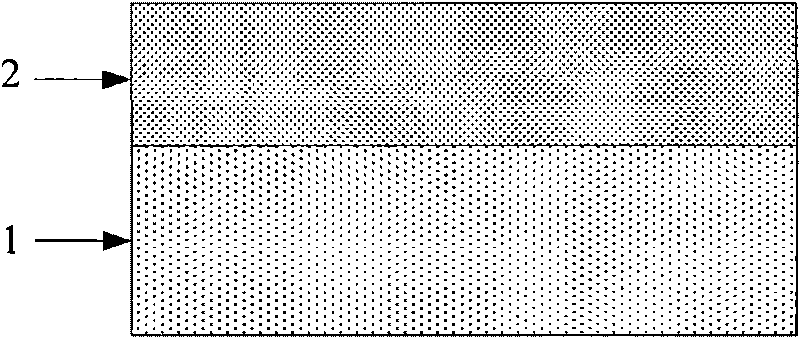

[0018] Step 1, see Figure 1a , doping N-type impurities on the P-type silicon substrate 1 to form an N-type channel 2 . Commonly used N-type impurities include phosphorus, arsenic, antimony, and the like. The doping method can be thermal diffusion or ion implantation.

[0019] After the N-type channel 2 is formed, threshold voltage adjustment implantation (not shown) can also be performed. That is to inject N-type or P-type impurities into the N-type channel 2 to change the impurity concentration of the N-type channel 2 . Since the threshold voltage of the MOS device is very sensitive to the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com