Window type semiconductor packaging structure capable of avoiding stripping in mold flow inlet

A technology of semiconductor and mold flow, which is applied in the direction of semiconductor devices, semiconductor/solid-state device components, electric solid-state devices, etc. It can solve problems such as stress deformation or peeling, affecting the reliability of finished products and manufacturing pass rate, and narrow mold flow entrance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] Embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. However, it should be noted that these drawings are simplified schematic diagrams, and are only used to illustrate the basic structure or implementation method of the present invention, so only those related to the present invention are shown. The components shown are not drawn with the number, shape and size ratio of the actual implementation. Some size ratios and other related size ratios have been modified, enlarged or simplified to provide a clearer description. The number, shape and size of the actual implementation The size ratio is an optional design, and the detailed component layout may be more complicated.

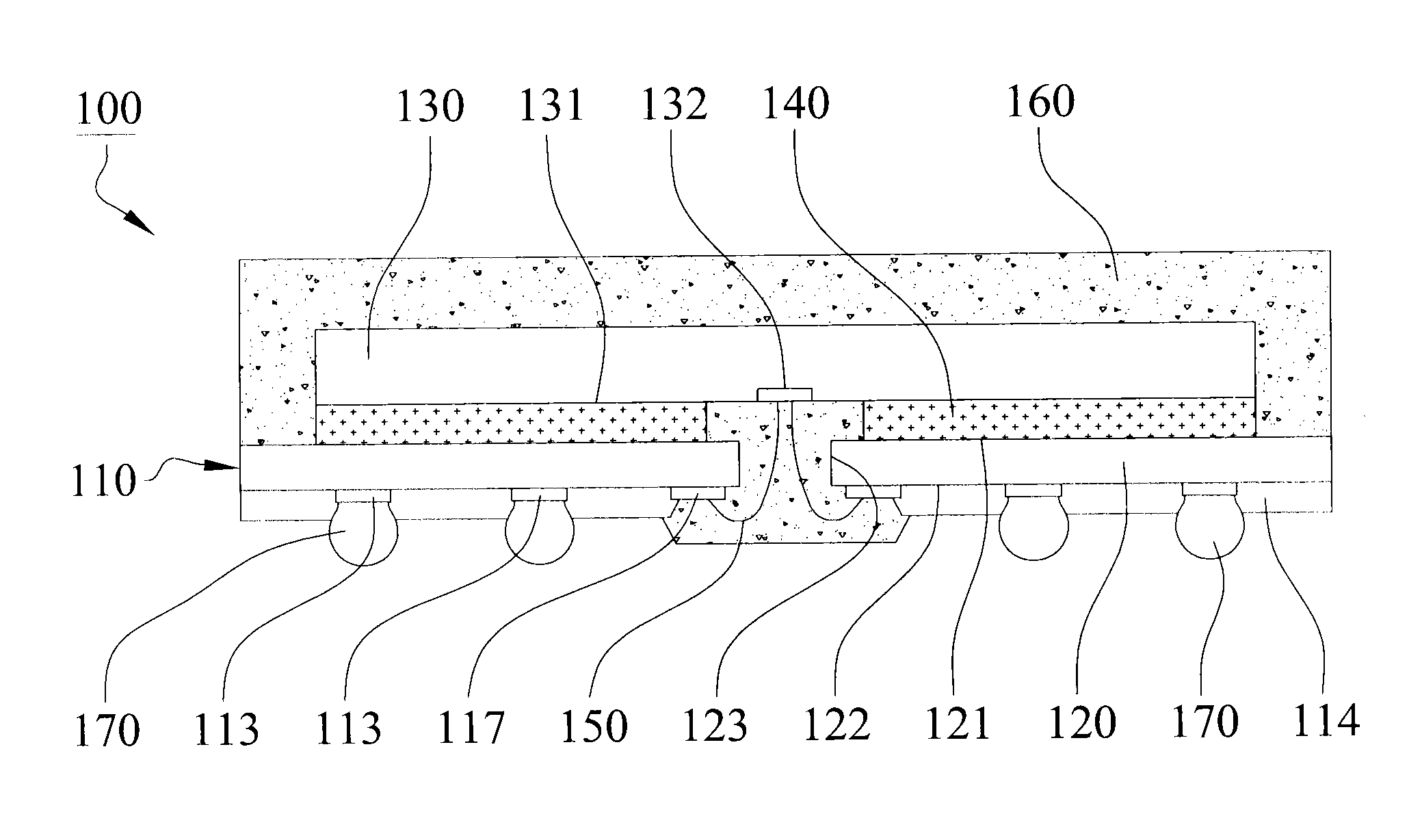

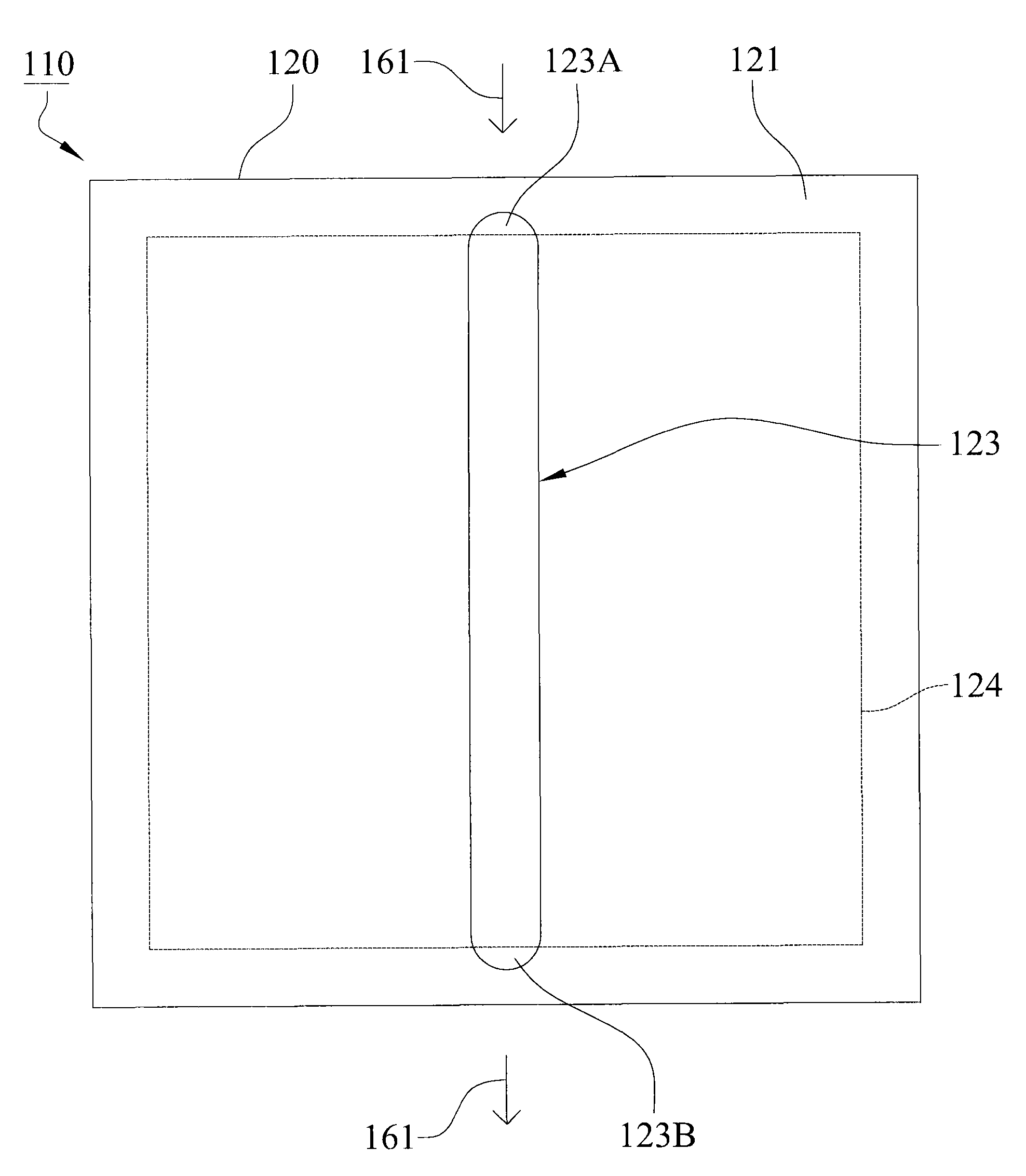

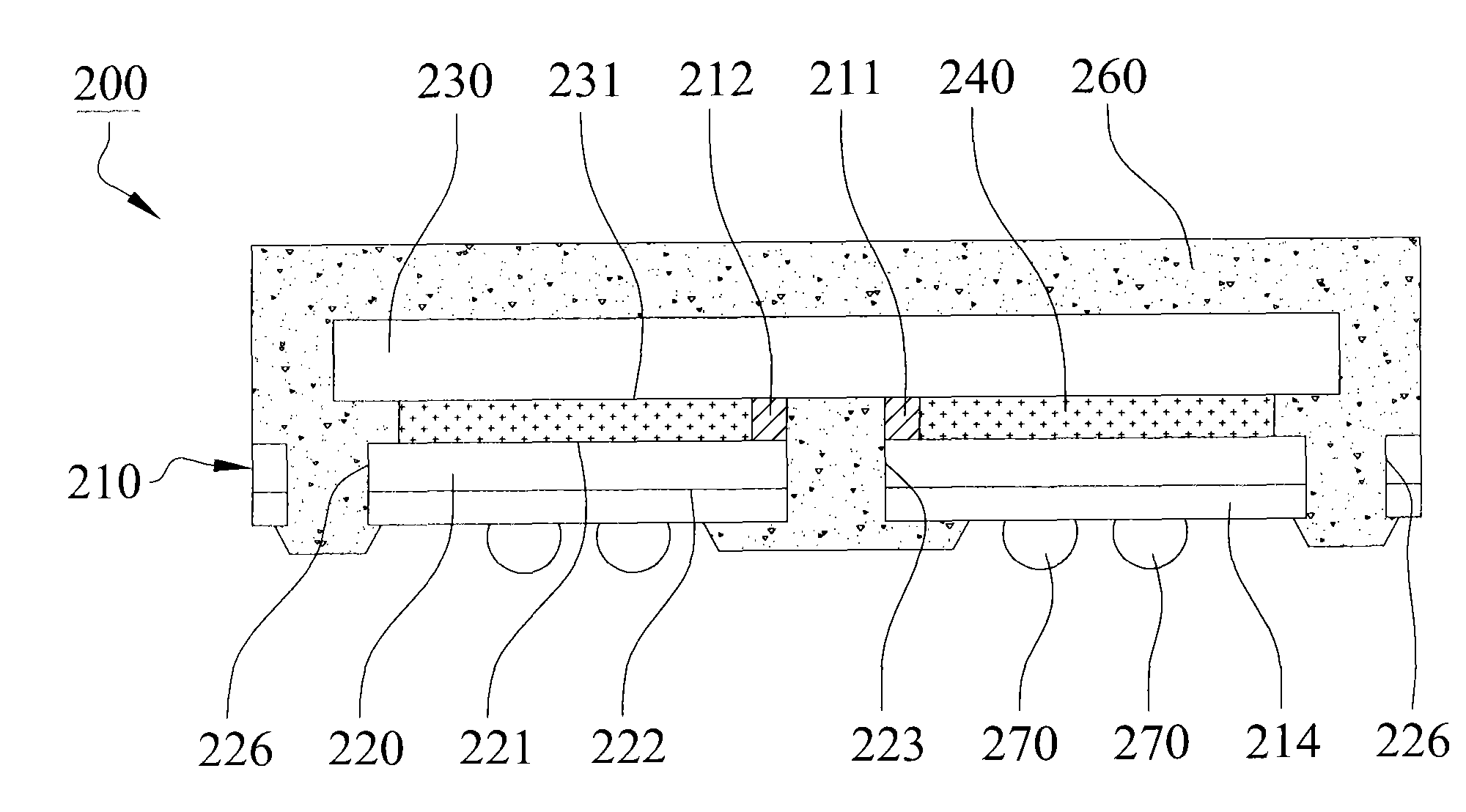

[0051] According to a specific embodiment of the present invention, a window-type semiconductor package structure that avoids mold flow inlet peeling is illustrated in image 3 Schematic cross-section of the die flow inlet cut along the sid...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com