Preparation method of low thermal resistance thermal interface

A technology of thermal interface and low thermal resistance, which is applied in chemical instruments and methods, heat exchange materials, semiconductor/solid-state device manufacturing, etc., can solve the problems of not very obvious effect and high thermal resistance of interface contact, and achieve strong implementability, The effect of reducing the contact thermal resistance of the interface and increasing the contact probability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

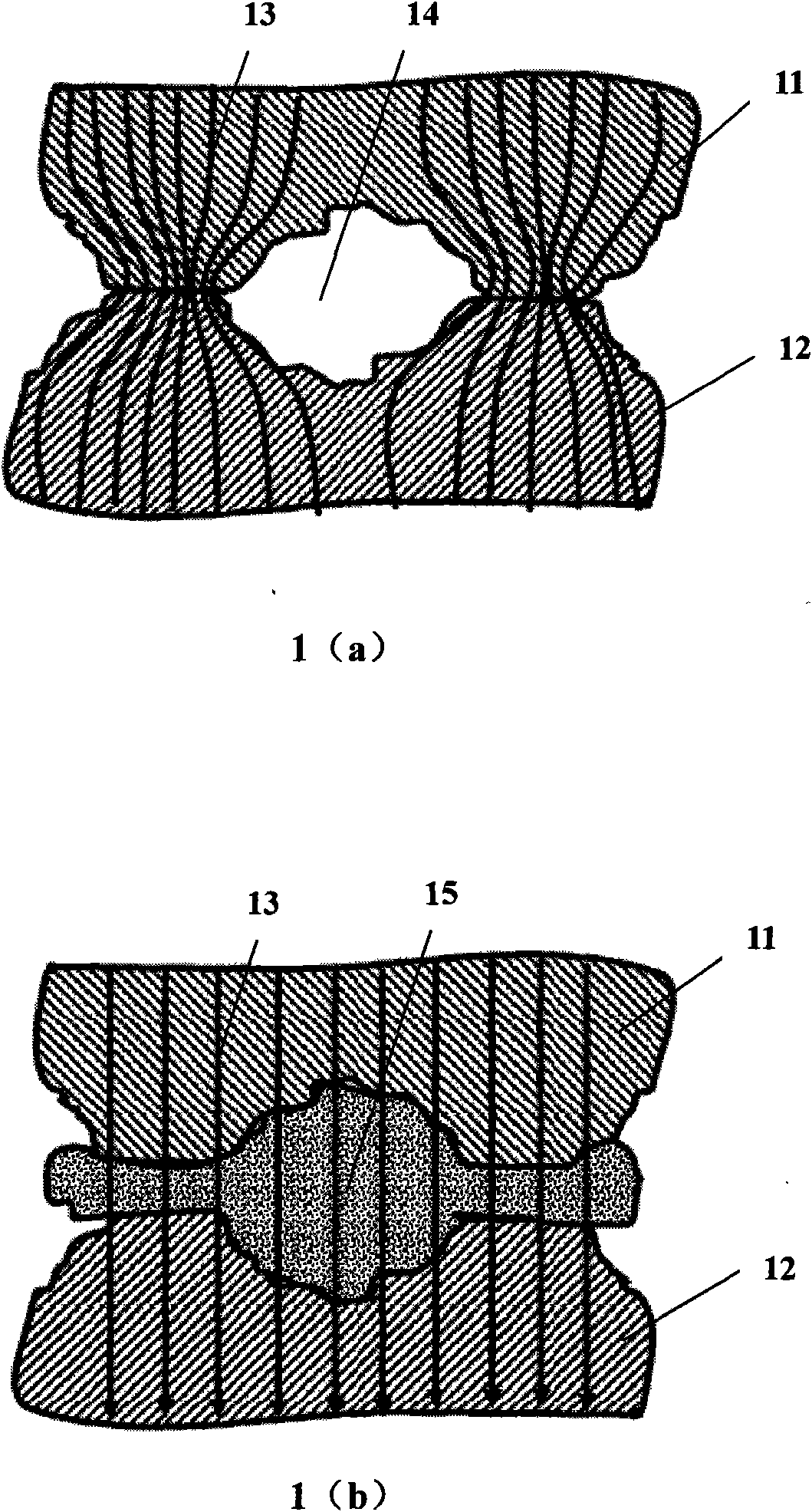

Image

Examples

Embodiment 1

[0024] 1. Catalyst deposition: adopt atomic layer deposition (ALD) technology to deposit 10 nanometer thick Ni or Fe layer on copper substrate 21, as the catalyst layer 22 of CNT growth;

[0025] 2. Catalyst cracking: using a high temperature annealing process at a temperature of 650°C to crack the catalyst layer 22 into catalyst particles 23;

[0026] 3. Growth of carbon nanotubes: using chemical vapor deposition (CVD) technology to prepare oriented growth carbon nanotubes (VACNT) 18 on the copper substrate 21, with a diameter of about 20 nanometers and a thickness of about 20 microns;

[0027] 4. VACNT modification: using water vapor etching technology to remove the catalyst particles 23 remaining on the top of VACNT 18, and at the same time reduce the winding of the top of VACNT;

[0028] 5. Deposition of magnetic material layer: deposition techniques include evaporation, sputtering, atomic layer deposition (ALD) and other thin film deposition techniques. The magnetic mater...

Embodiment 2

[0035] 1. The copper substrate 21 for growing carbon nanotubes is replaced with a silicon substrate 33, and other VACNT magnetization processes are the same as in Embodiment 1, including catalyst deposition and cracking, carbon nanotube growth and modification, magnetic material layer deposition and heat treatment;

[0036] 2. Electromagnetic alignment: see Figure 9 Place the silicon substrate 33 grown with VACNT18 in the middle of the induction coil 34, turn on the high-frequency power supply 35, and under the action of the electromagnetic field 36, the magnetic particles 26 at the top of the VACNT 18 are subjected to magnetic force, so that the VACNT 18 are parallel to each other;

[0037] 3. Solder bonding: After depositing metal titanium and tin layer 38 (wherein the thickness of the titanium layer is 20 nanometers, and the thickness of the tin layer is 5 microns) on the lower surface of the gallium nitride (GaN) substrate 37, it is placed on a substrate grown with VACNT24...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Diameter | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com