Thin film semiconductor device fabrication method and thin film semiconductor device

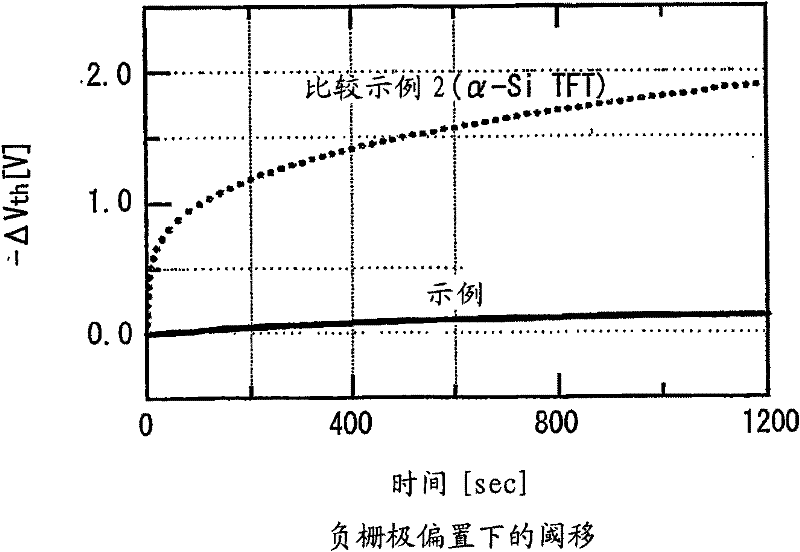

A technology of thin-film semiconductors and manufacturing methods, which is applied in the manufacture of bottom-gate thin-film semiconductor devices and in the field of thin-film semiconductor devices. It can solve problems such as threshold shift, difficulty in maintaining film quality, and reduced mobility, and achieve fine-scale effects.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

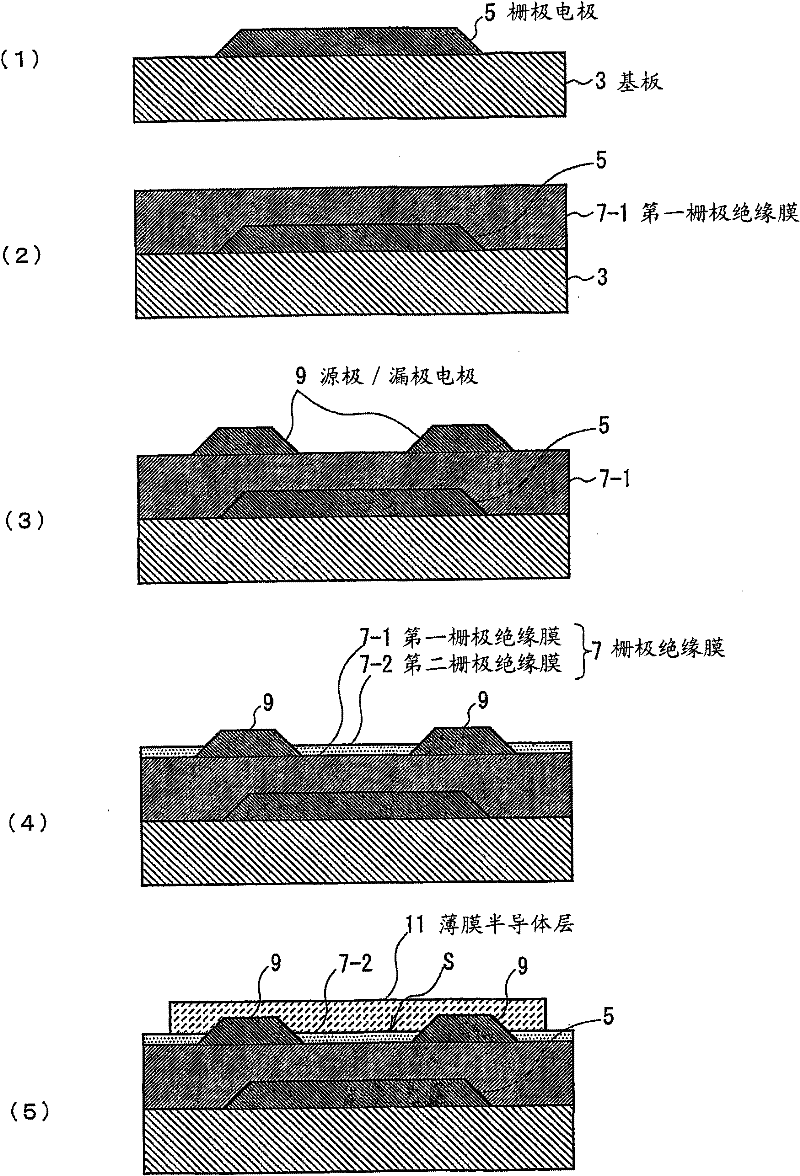

[0017] First, like figure 1 As shown in (1), a substrate 3 is provided. Here, plastic substrates such as polyethylene terephthalate (PET), polyethersulfone (PES), polyethylene naphthalate (PEN), etc., and glass substrates are used. Or stainless steel substrate.

[0018] The gate electrode 5 is formed on the substrate 3. For example, the formation of the gate electrode 5 is performed by forming a metal film and patterning and etching the metal film using a resist pattern formed by photolithography as a mask. The metal film can be formed by a film forming method suitable for the material.

[0019] In the case of metal films such as Al, Cu, Au, Ni, W, Mo, etc., sputtering deposition can be used. In addition, in the case of metal films such as Au, Ag, Ni, Pd, Cr, etc., plating deposition and vapor deposition can be used. Then, after patterning and etching the metal film using the resist pattern as a mask, the resist pattern is removed. The finer gate electrode 5 can be formed usi...

no. 2 example

[0038] The second embodiment is that the first gate insulating film 7-1 formed in the first embodiment is changed to include an inorganic insulating film (for example, silicon oxide (SiO x ), silicon nitride (SiN x ) Etc.) and an example of a multilayer structure of an organic insulating film on an inorganic insulating film, and the other structures are the same as in the first embodiment.

[0039] Silicon oxide (SiO) with particularly high stability to gate leakage and electrical current stress x ), silicon nitride (SiN x ) Etc. are preferably used as the inorganic insulating film. The inorganic insulating film is formed by sputtering or plasma enhanced CVD (PECVD: Plasma Enhanced Vapor Chemical Deposition). In addition, the organic material constituting the first gate insulating film 7-1 described in the first embodiment is used as the organic insulating film, and similarly, it is preferable to use a material having particularly high adhesion to the source / drain electrodes 9 Po...

no. 3 example

[0043] The third embodiment is to selectively form the film in the first embodiment through film formation by coating. figure 1 (4) The described method of the second gate insulating film 7-2. Use below figure 1 To describe the manufacturing method of the third embodiment.

[0044] First, as described in the first embodiment, perform figure 1 (1) and figure 1 The step shown in (2) is to form the gate electrode 5 on the substrate 3 and cover the gate electrode 5 with a first gate insulating film 7-1 composed of an organic material. Similarly, polyimide, PVP, poly(α-methylstyrene), etc., which have particularly high adhesion to the source / drain electrodes 9 and have a stable surface state are preferable as the first gate insulating layer. Organic material of film 7-1.

[0045] Then, when figure 1 (3) When forming the source / drain electrode 9 on the first gate insulating film 7-1 in the step shown, use a material that is compatible with the material used to form the second gate ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com