Sputtering apparatus and method for producing semiconductor device with the same

A sputtering device and semiconductor technology, applied in semiconductor/solid-state device manufacturing, sputter coating, electrical components, etc. Substrate short circuit and other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

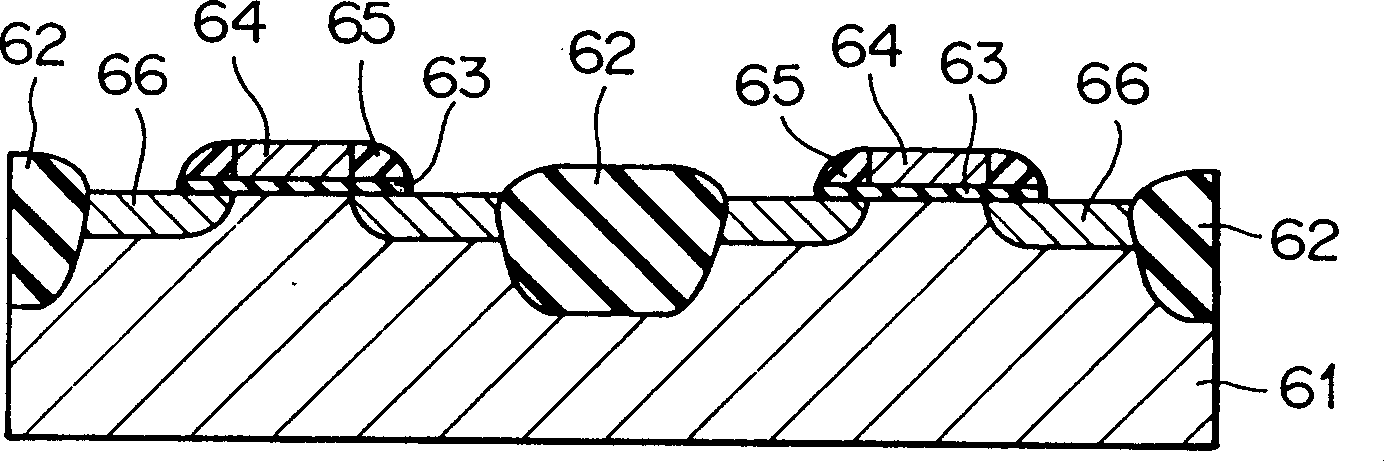

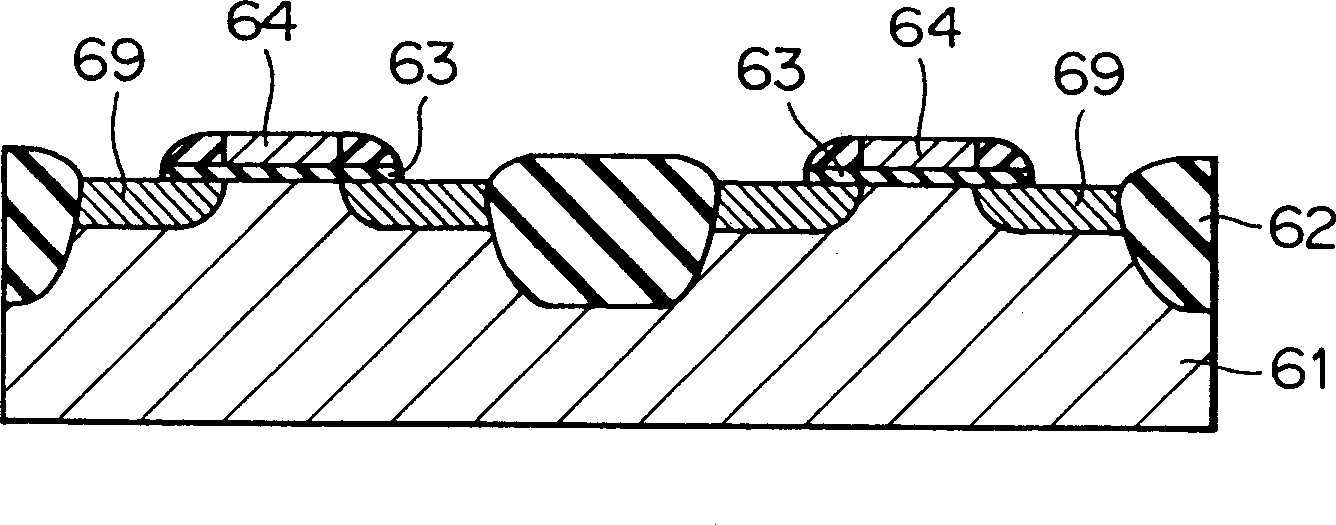

[0029] As a result of concentrated and continuous experiments and research conducted to solve the above-mentioned problems, it has been shown that the gate oxide film can be prevented from drop in initial withstand voltage.

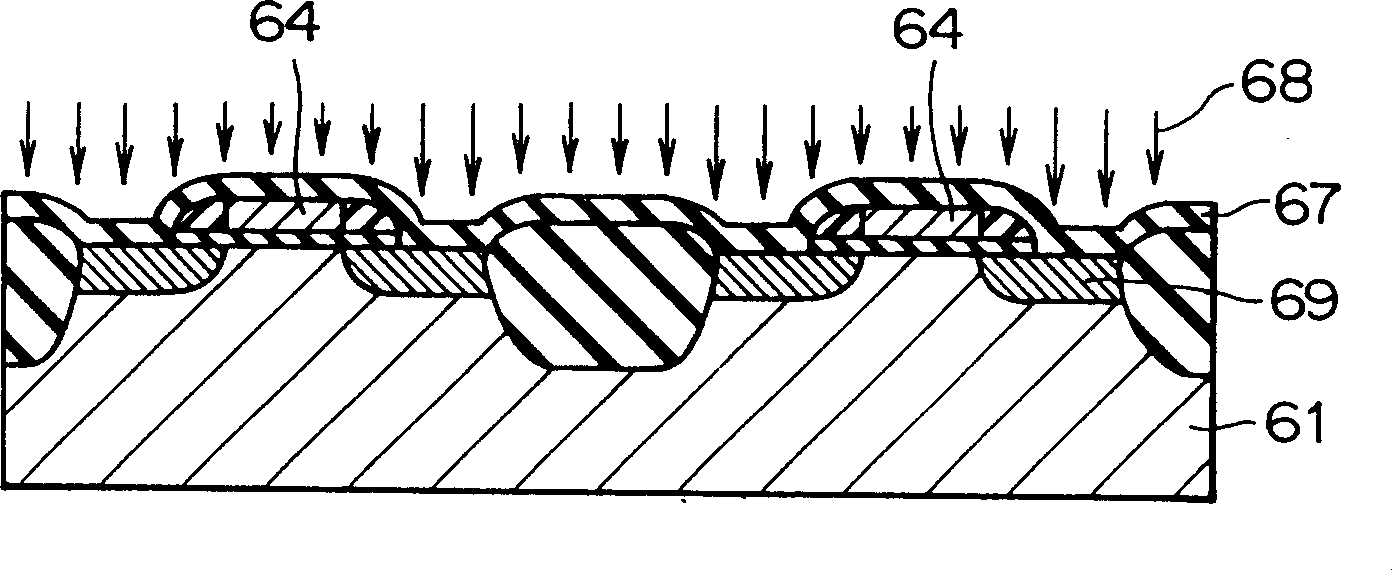

[0030] When a plasma discharge occurs in a conventional DC magnetron sputtering device, the removal of Ar + In addition to ions 97, there are also electrons 99, as shown in Figure 3. Also, in Ar + When the ions 97 collide with the titanium target 83 and bombard the titanium particles 98, a very small amount of electrons 99 are also generated in the plasma. These electrons 99 reach the wafer 86 mounted on the wafer holder 77 in an electrically floating state under the action of the vertical magnetic field generated by the cathode magnet 82 . It is clear that these electrons 99 damage the gate oxide film, resulting in a drop in the initial withstand voltage.

[0031] Damage to the gate oxide film by electrons 99 occurs shortly before the titanium film i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com