Instruction combination filtration method and system for instruction grade stochastic verification

A technology of instruction combination and random verification, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve problems such as error debugging process, repeated coverage, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

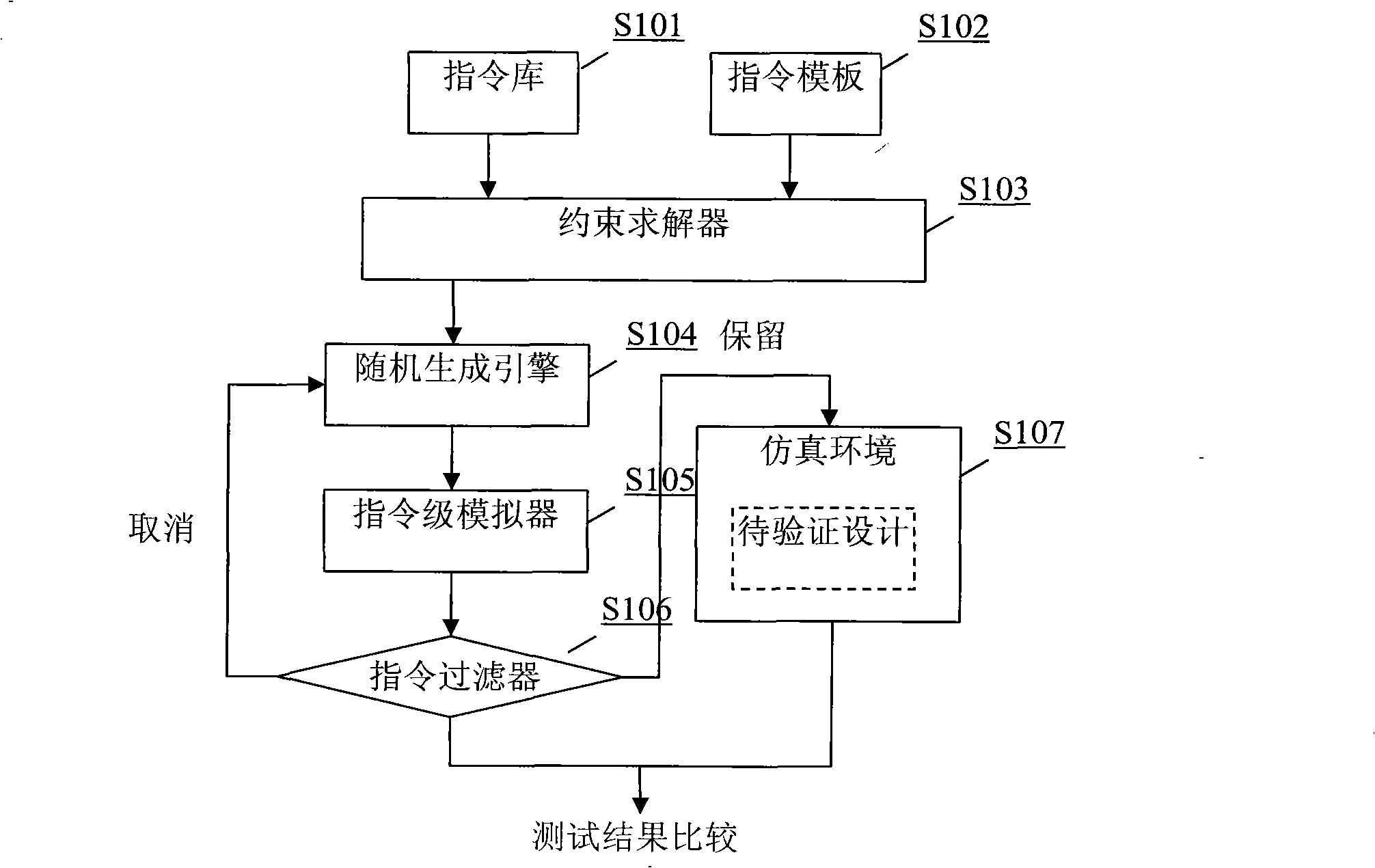

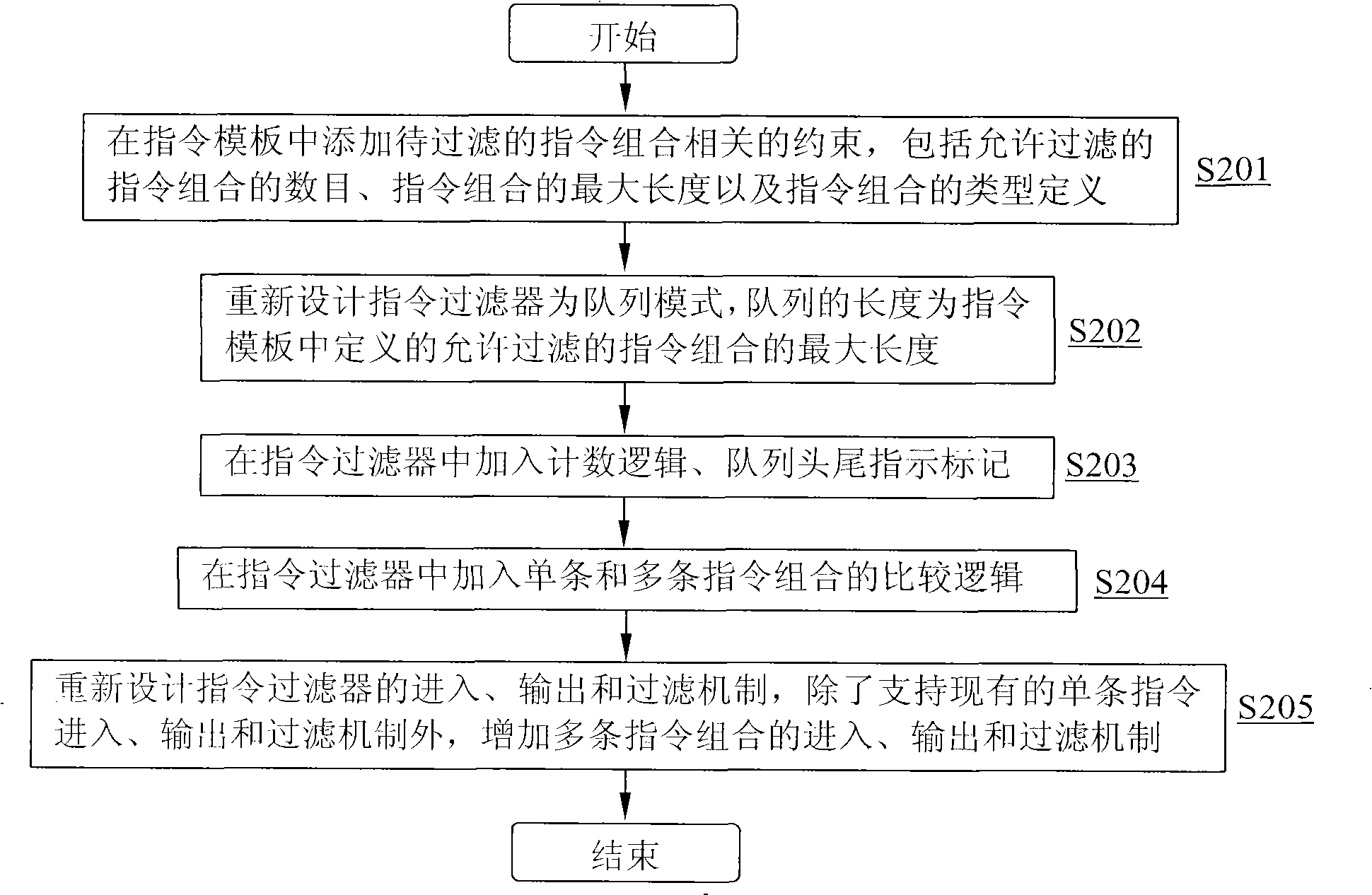

[0048] The instruction combination filtering method for instruction-level random verification of the present invention is realized through the following technical solutions, specifically including:

[0049] Step 1, add constraints related to the instruction combination to be filtered in the instruction template, including the number of instruction combinations allowed to be filtered, the maximum length of the instruction combination, and the type definition of the instruction combination;

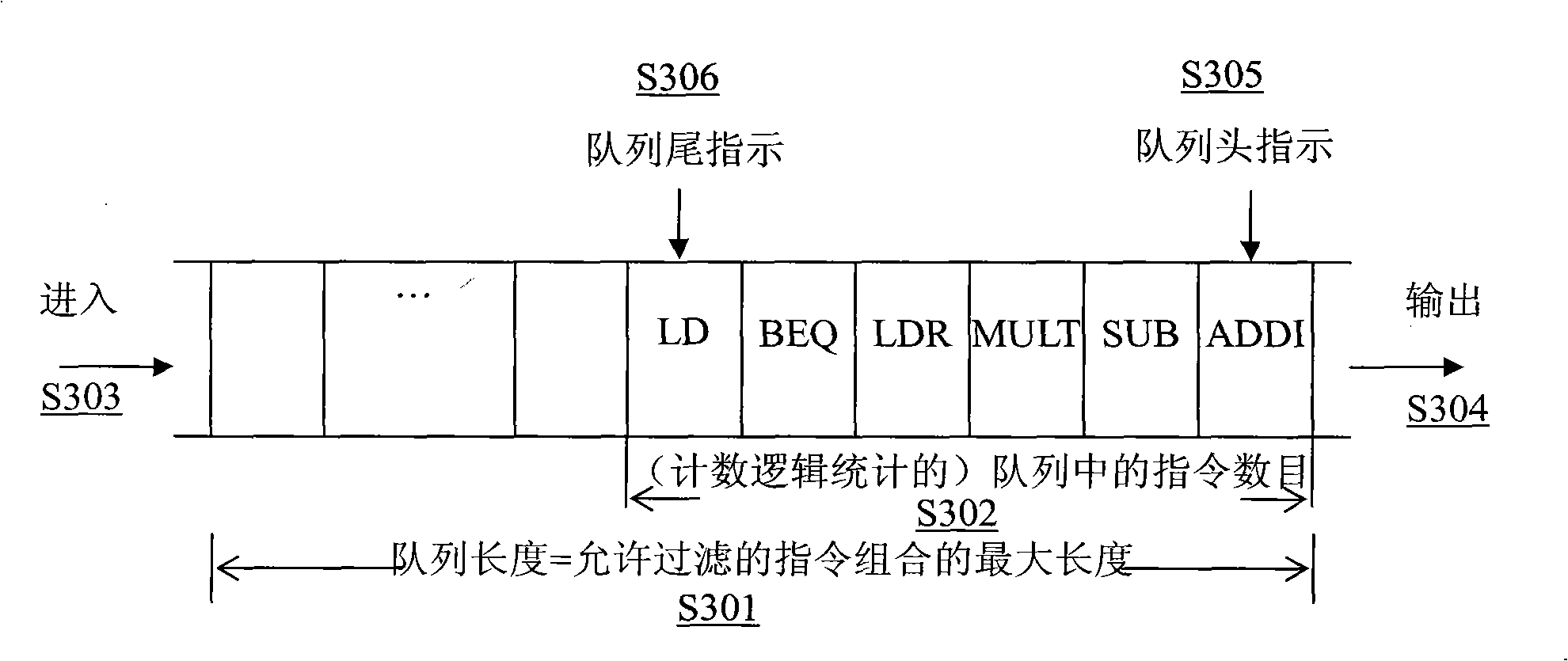

[0050] Step 2, redesign the instruction filter to queue mode, and the length of the queue is the maximum length of the instruction combination allowed to be filtered defined in the instruction template in step 1;

[0051] Step 3, adding counting logic and queue head and tail indicators to the command filter;

[0052] Step 4, adding comparison logic of single and multiple instruction combinations in the instruction filter;

[0053] Step 5, redesign the entry, output and filtering mechanism ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com