Data transmitting and receiving method and device based on processor sharing internal memory

A data transmission method and technology of a data transmission device, which are applied in the directions of multi-programming devices, electrical digital data processing, instruments, etc., can solve the problems of repeated copying of message data, and achieve the effect of reducing overhead.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

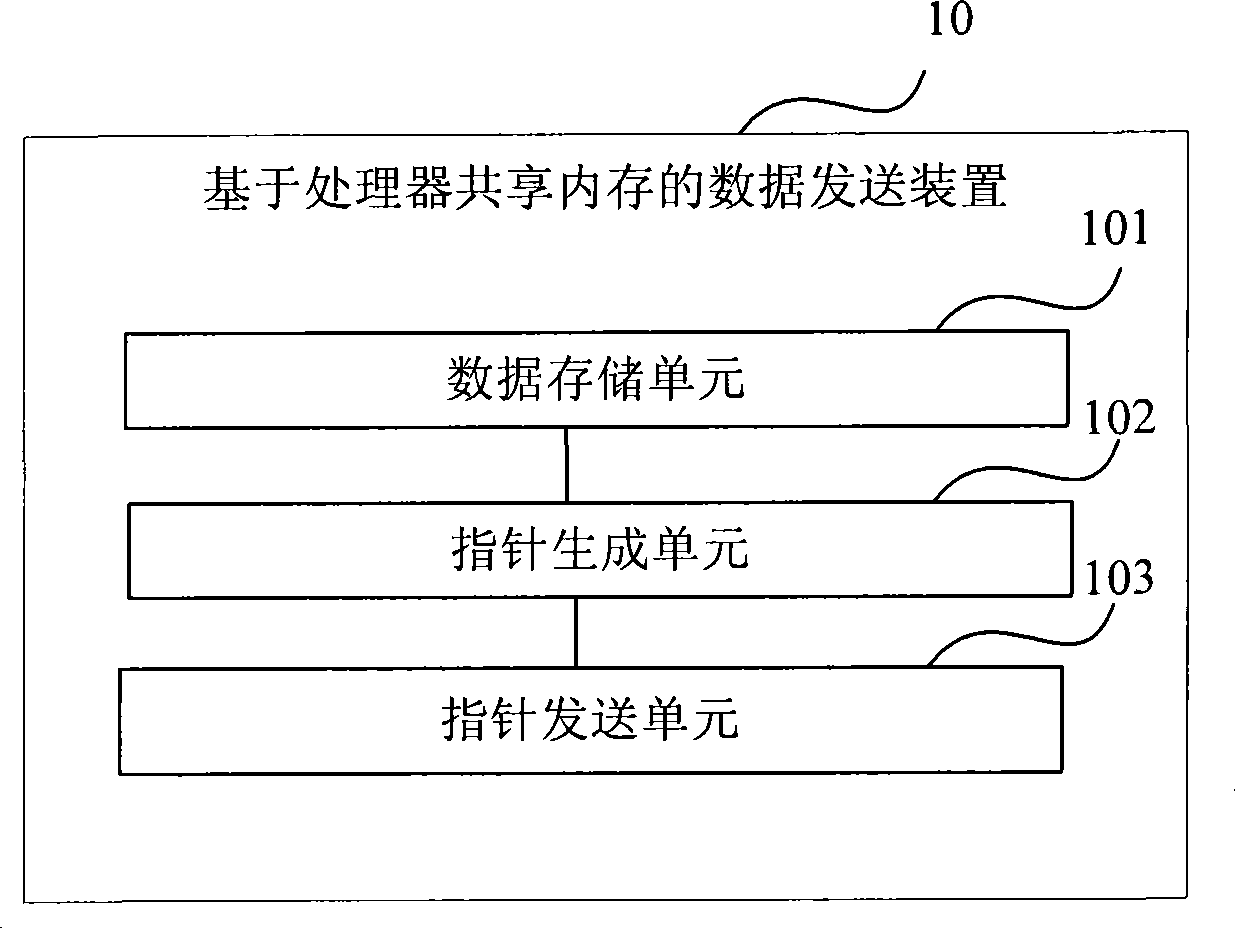

[0028] Such as figure 1 As shown, it is a schematic block diagram of a message transmission device based on processor shared memory according to an embodiment of the present invention. The data sending device 10 includes: a data storage unit 101, which is used to write data into at least one of the shared memory pools of the processor. A memory block; a pointer generating unit 102, configured to generate a memory block pointer according to the address information of the memory block; a pointer sending unit 103, configured to send the memory block pointer to a receiver.

[0029] If device 10 sends a message broadcast:

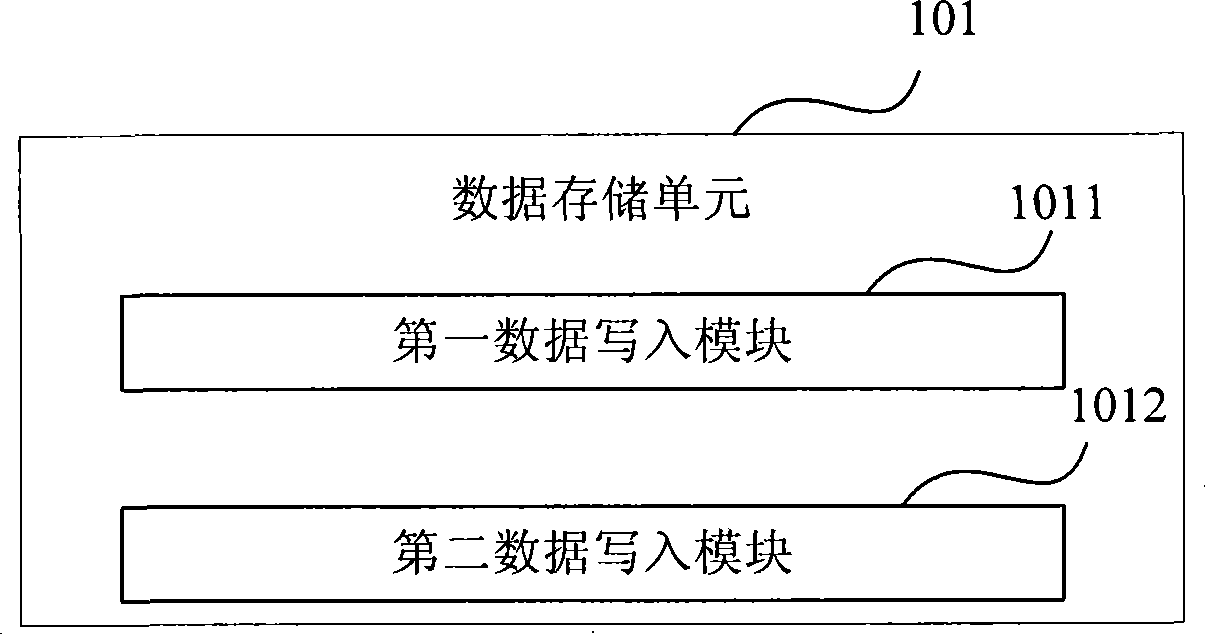

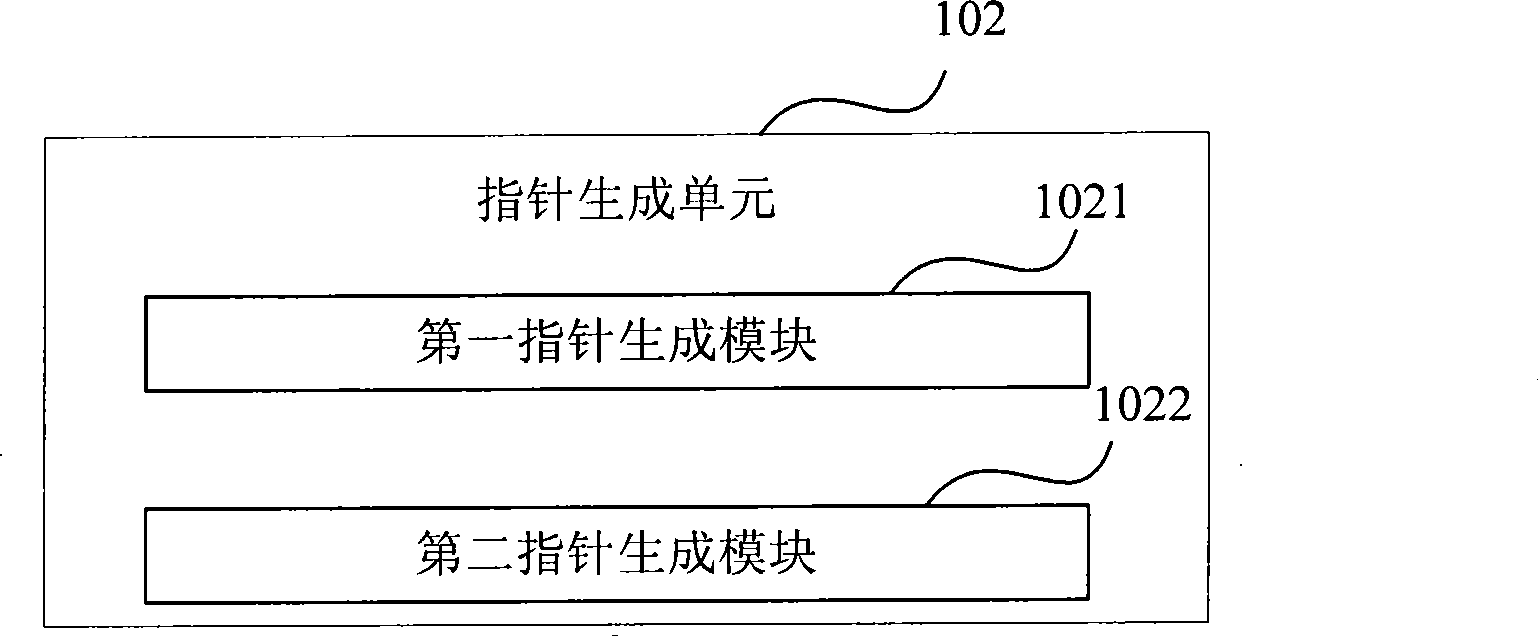

[0030] Such as figure 2 As shown, the data storage unit 101 may include a first data writing module 1011: used to obtain a memory block from the memory pool as a message buffer, and write the message data to be sent into the data area in the message buffer; image 3 As shown, the pointer generation unit 102 may include a first pointer generation module 1021: ...

Embodiment 2

[0053] The embodiment of the present invention includes the following two parts: a queue structure in which message queues and buffers are separated, and is used for high-speed message broadcasting.

[0054] The queue structure of message queue and buffer separation is as follows Figure 9shown. The message queue is a message buffer pointer queue in the form of a linked list, and the queue pointer in the task control block points to the message queue. A message buffer consists of a message header and a data area. Wherein, in addition to recording the message name, message type, data volume and sending task identifier, the message header also includes a lifetime. The lifetime records the number of times the message is sent.

[0055] In a multi-core processor system, the above-mentioned queue structure is located in the shared memory space. In this way, not only messages can be passed between tasks of the same core, but also message communication can be adopted between tasks...

Embodiment 3

[0064] The embodiment of the present invention includes the following three parts: a message queue, a queue structure in which a message header and a data buffer are separated, and is used for high-speed message forwarding.

[0065] Such as Figure 11 shown, shows that in the second embodiment Figure 9 Based on the queue structure that further separates the message header and the data buffer, both the message header and the data buffer occupy memory blocks independently. Among them, in addition to including the message name, message type, data volume, sending task identification and lifetime, the message header also adds two pointers: data buffer pointer and parent message pointer. The parent message pointer is used for the forwarded message to point to its parent message.

[0066] High-speed message forwarding also consists of four processes of message creation, sending, receiving and releasing.

[0067] The message creation process obtains two memory blocks from the memo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com