Load bearing belt for packing chip and chip packaging structure

A chip packaging structure and carrier tape technology, applied in electrical components, electrical solid-state devices, circuits, etc., can solve problems such as poor production and testing efficiency, large process time, and carrier tape waste.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

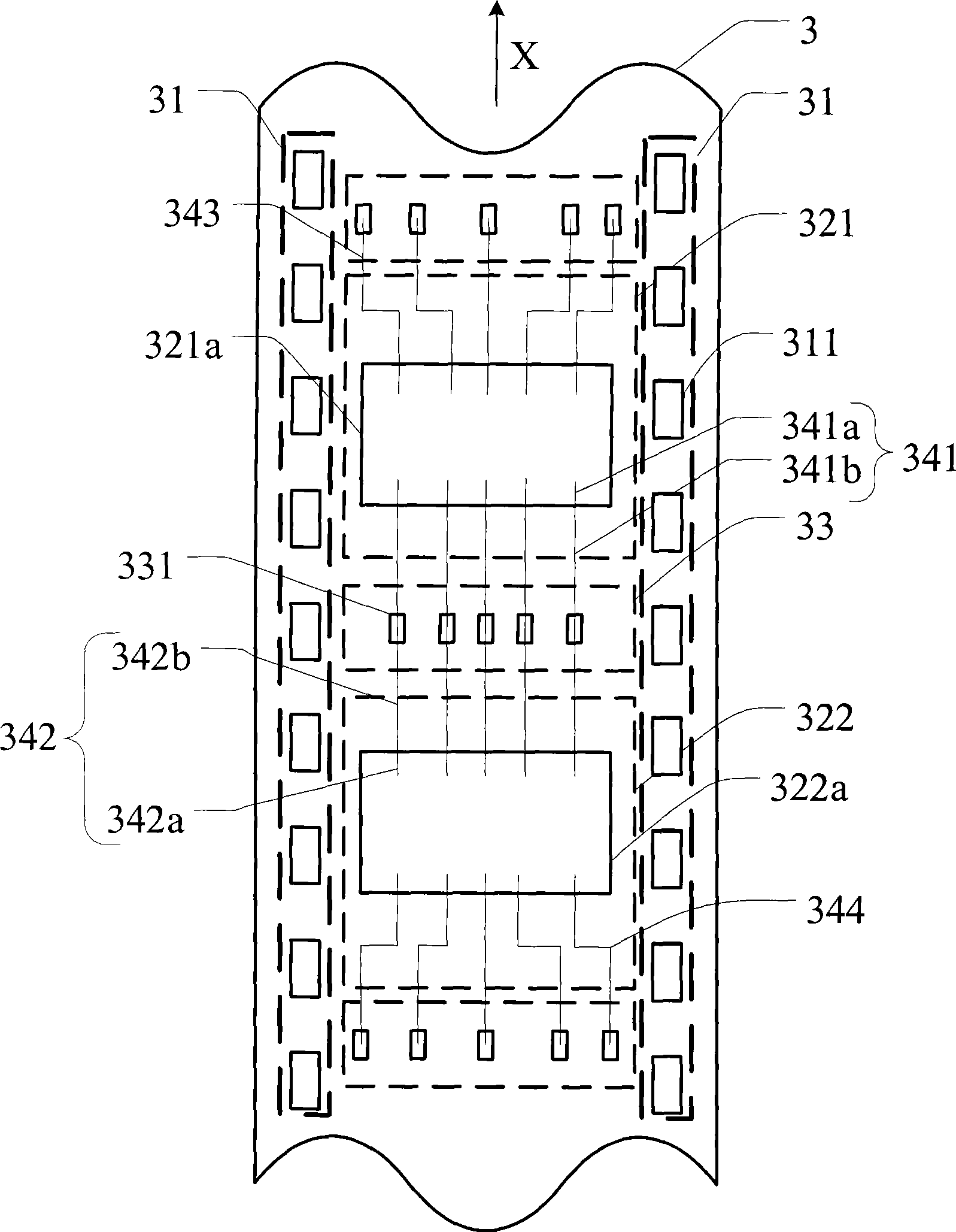

[0034] An embodiment of the present invention discloses a carrier tape 3 for packaging chips, which can extend along a conveying direction X, such as figure 2 As shown, the carrier strip 3 at least includes two transmission areas 31 , two packaging areas 321 and 322 , a test pad area 33 , a plurality of test pads 331 disposed on the test pad area 33 and a metal circuit layer.

[0035] In this embodiment, the two transmission areas 31 of the carrier belt 3 are respectively defined on the two sides of the carrier belt 3 and extend along the conveying direction X. , and adjacent to a plurality of positioning holes 311 disposed on two sides of the carrier belt 3 . The carrier tape 3 is transported and positioned through the positioning hole 311. For example, when the carrier tape 3 is positioned at one position, it is suitable for chip packaging, and then positioned at another position for cutting.

[0036] For convenience of description, the encapsulation areas 321 and 322 can ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com