Method for preparing transistor T type nano grid

A manufacturing method and transistor technology, which are applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of difficult process realization and extremely high requirements for overlay accuracy, and achieve easy control of development time, high reliability, and high reliability. simple craftsmanship

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

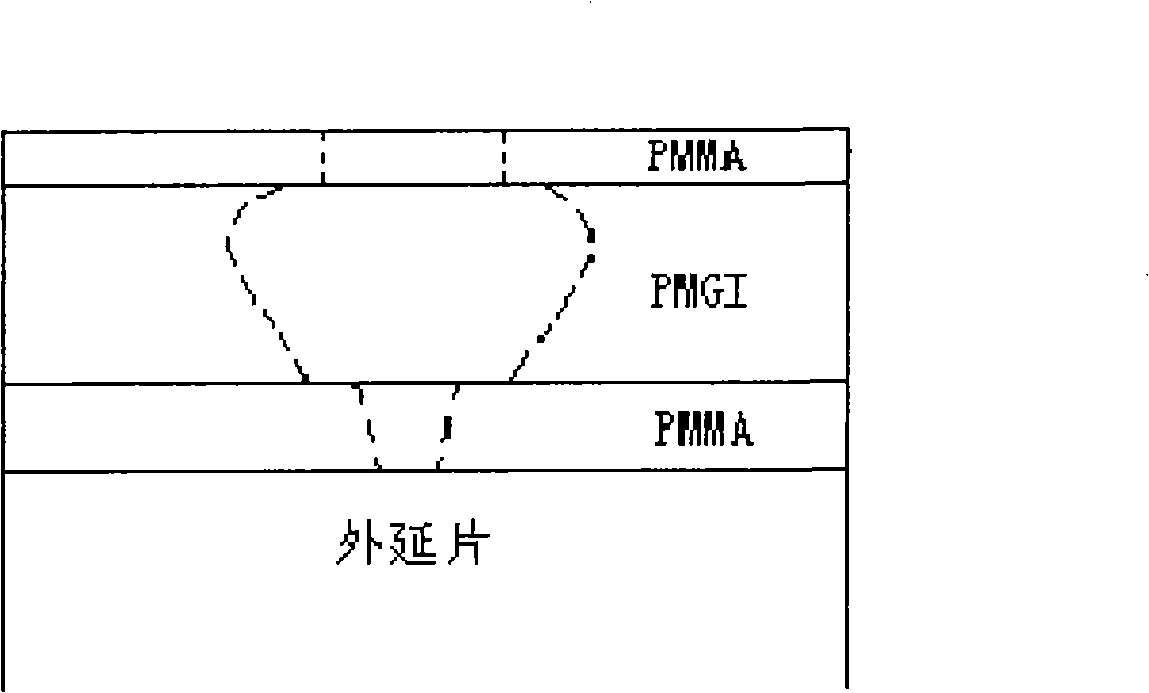

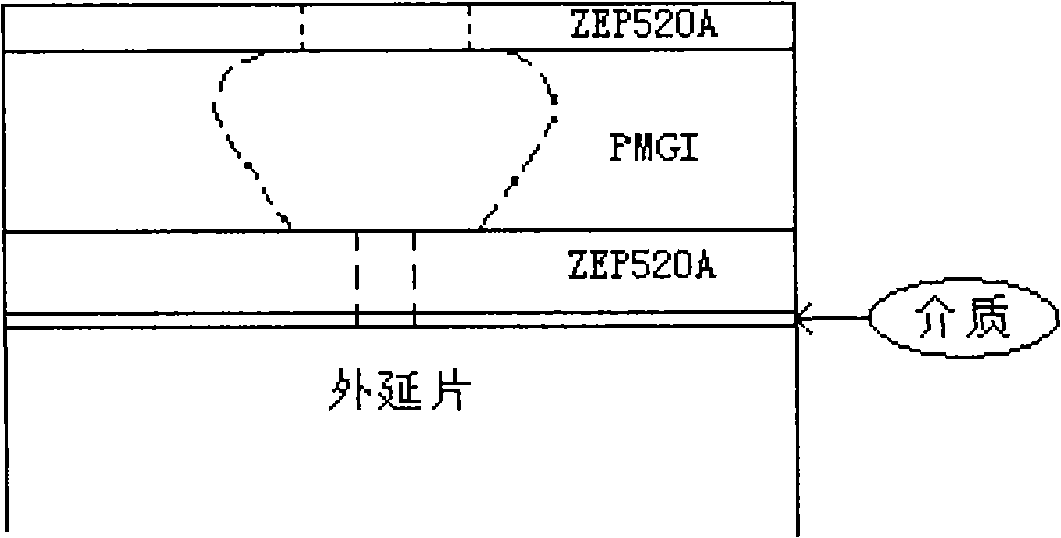

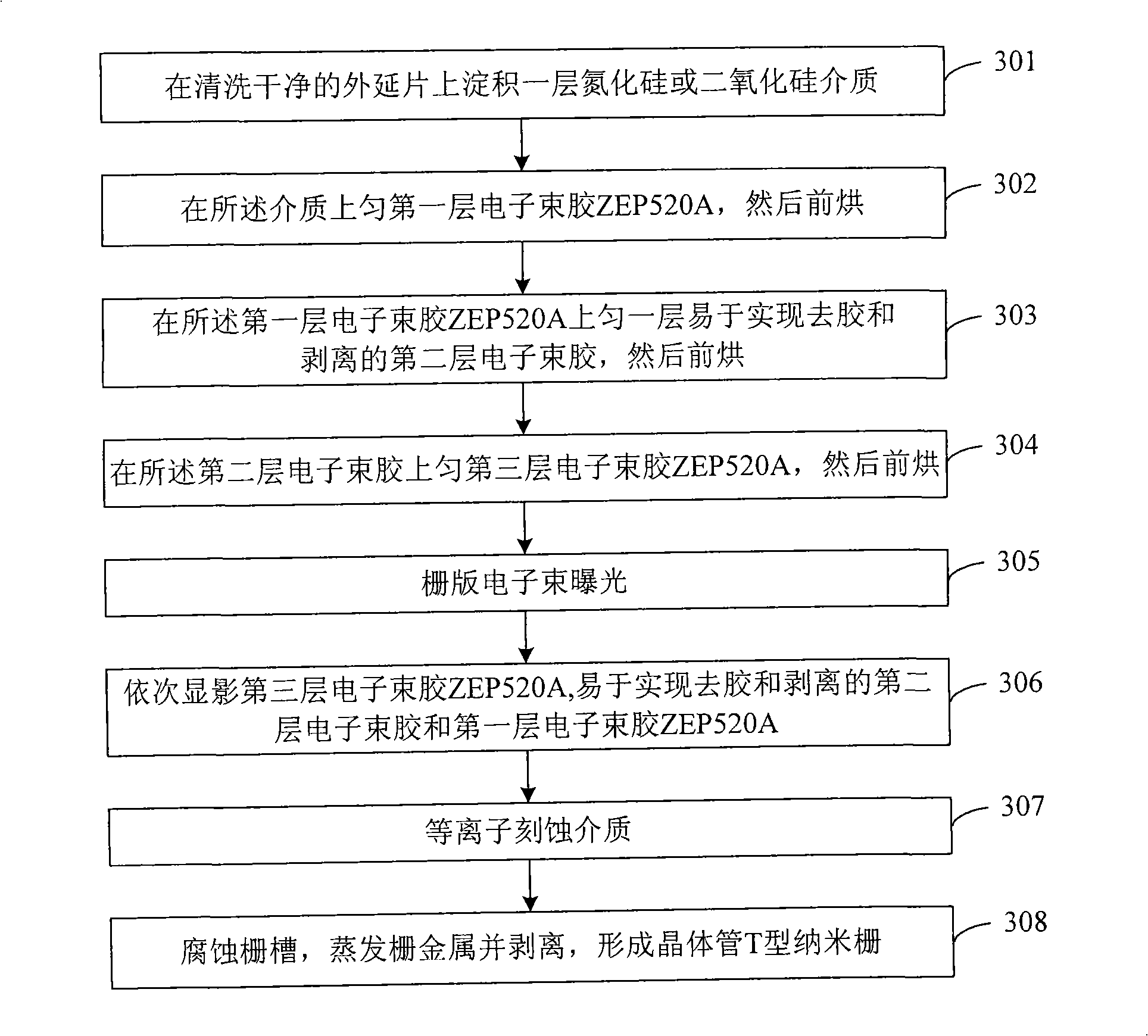

[0070] The method for fabricating the T-type nano-gate of the high electron mobility transistor (HEMT) in this embodiment is to address some shortcomings in the production of the T-type nano-gate of the high electron mobility transistor (HEMT) at present, using ZEP520A / PMGI / ZEP520A three-layer electron beam The photoresist structure (as shown in Table 1) and one electron beam exposure method are used to fabricate the T-type nano-gate of high electron mobility transistor (HEMT).

[0071] Table 1 is a schematic diagram of the structure of the ZEP520A / PMGI / ZEP520A three-layer electron beam photoresist used in the method for manufacturing the T-type nano-gate of the high electron mobility transistor (HEMT) of the present invention:

[0072]

[0073] Table 1

[0074] In this embodiment, the second layer of electron beam glue that is easy to remove and peel off is PMGI electron beam glue, and the ZEP520A / PMGI / ZEP520A three Layer electron beam photoresist structure, the role of e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com