Vertical stacking of multiple integrated circuits including SOI-based optical components

An integrated circuit, vertical stacking technology, applied in the direction of optical waveguide, light guide, etc., can solve problems such as wafer bending

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

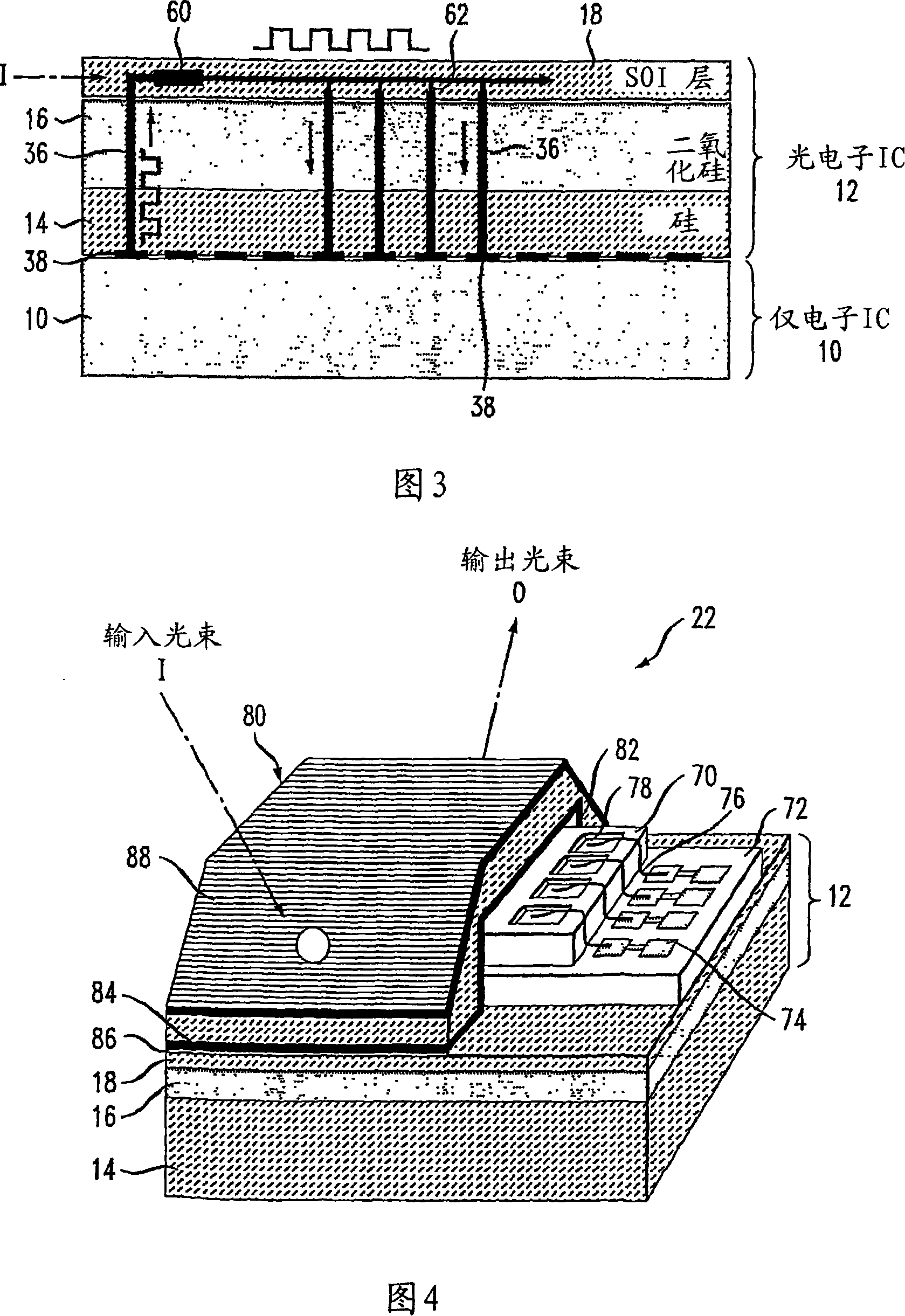

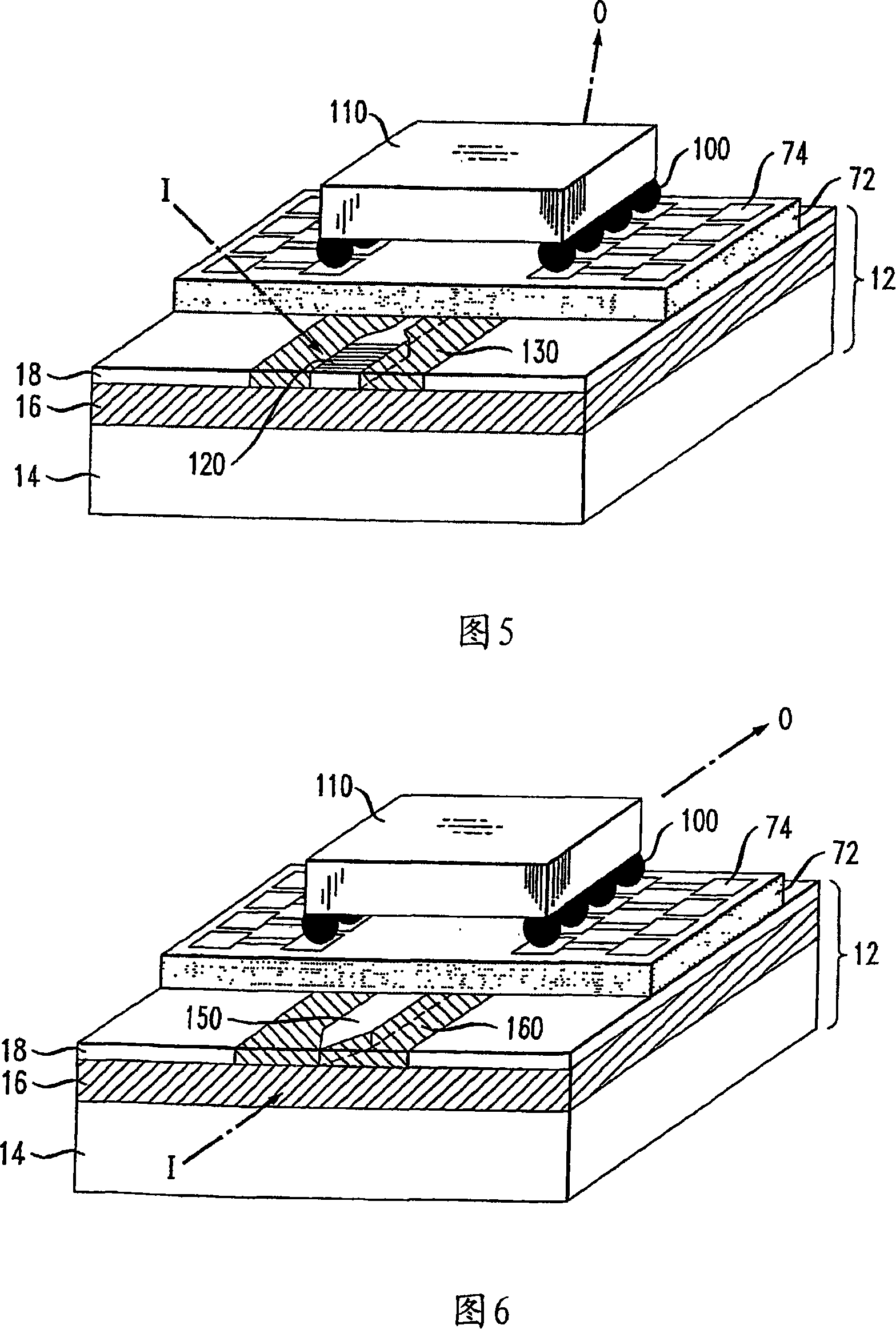

[0019] Figure 1 shows in cutaway side view a typical vertically stacked device formed in accordance with the present invention. As shown, the device includes a first integrated circuit (IC) 10 comprising electronic circuitry, wherein the IC 10 is fabricated using conventional CMOS processing techniques. In practice, fine linewidth lithography as described above can be used to form elements in IC 10 . An SOI-based optoelectronic circuit 12 is arranged above the electronic IC 10 in the manner shown in FIG. 1 . As is well known in the art, SOI-based circuitry 12 includes a base silicon substrate 14, a buried oxide layer 16, and a relatively thin silicon surface layer 18 (hereinafter "SOI layer"). Although not specifically illustrated in FIG. 1 for clarity, this layer may include differently doped regions and / or other sub-layers (e.g., polysilicon, interlevel dielectric, and metallization) needed to form the desired passive and active optical devices. ). For this particular emb...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com