Global compiler for controlling heterogeneous multiprocessor

一种多处理器、编译程序的技术,应用在编译程序领域,能够解决开发时间、有效性能不实用等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0061] One embodiment of the present invention will be described below with reference to the drawings.

[0062]

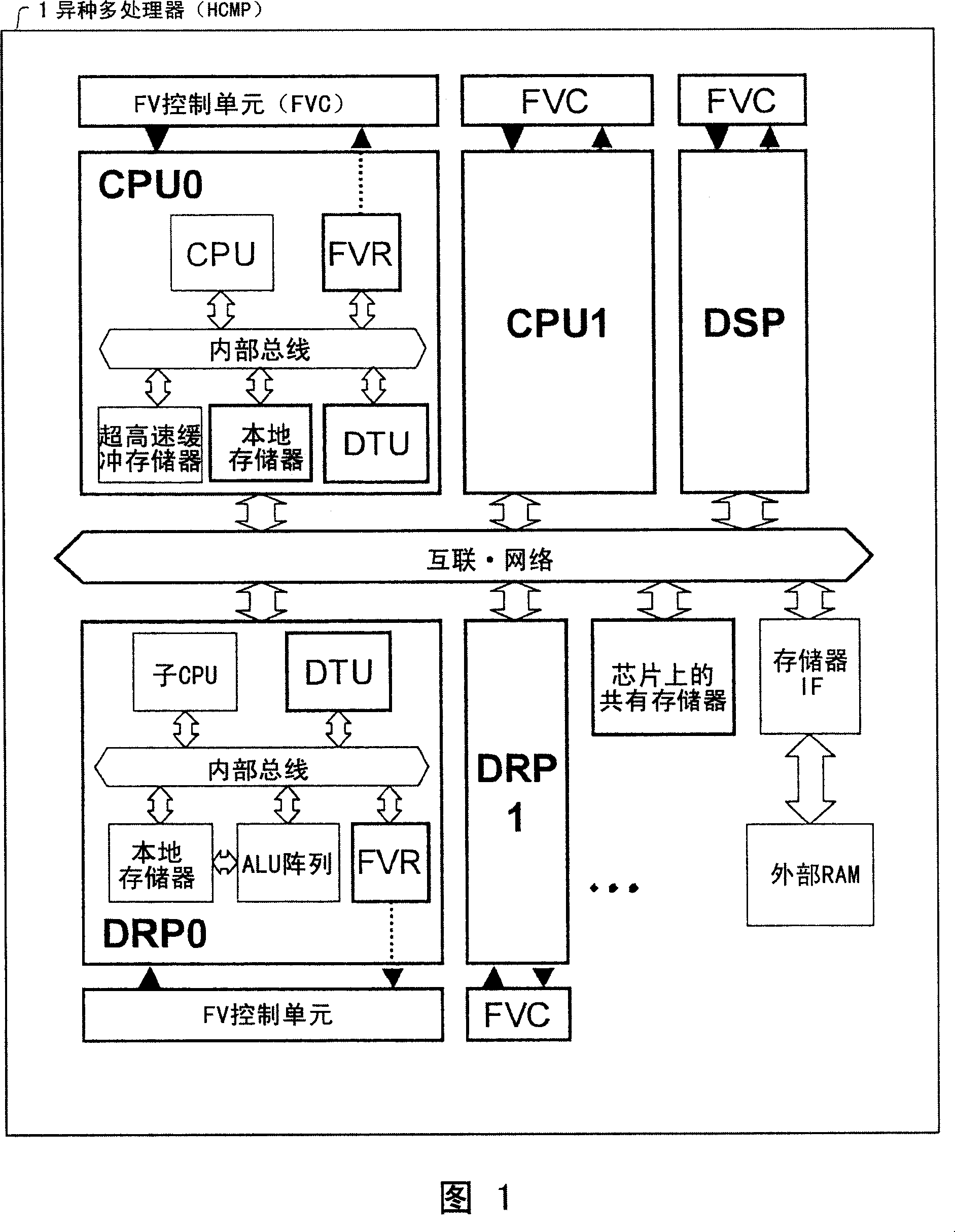

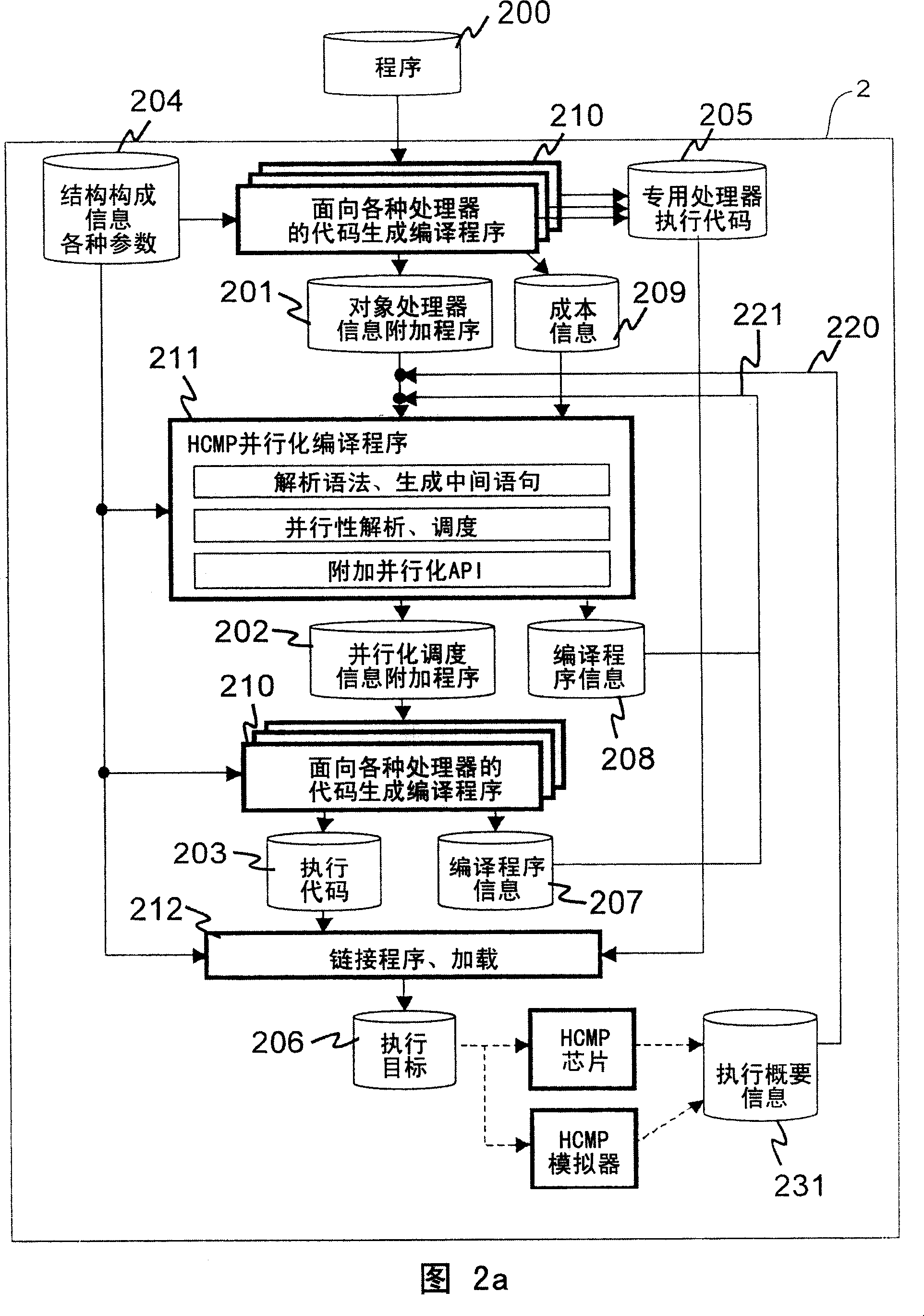

[0063] As an embodiment of the present invention, first, the configuration of a heterogeneous multiprocessor system (hereinafter, HCMP) 1 to which the parallel compilation method provided in the present invention is applied will be described with reference to the block diagram of FIG. 1 . In HCMP1, a plurality of heterogeneous processor units (PU) and shared memory (CSM) are configured. Each of these PUs is connected to an interconnection network (LBUS). In addition, the respective SMs are connected to the LBUS. Each PU is connected to a power supply voltage / clock frequency control circuit that supplies a power supply voltage and an operating clock to various parts such as a processor core and a memory of each PU. In this embodiment, the type and number of PUs are composed of two general processing processors (CPU), one signal processing processor (DSP), and tw...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com