Phase detetor and phase detecting method

A phase detector and phase detection technology, which can be used in circuits that oscillate independently of each other, automatic power control, digital transmission systems, etc., and can solve problems such as expensive and complex products.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The circuits disclosed below are preferably integrated in one or several integrated circuits. The high speed operation required by the position maintaining circuit, logic gates and circuit blocks are best implemented in CML logic with bipolar transistors. The best processing is the 0.4 μm bipolar processing suitable for digital circuits operating in the frequency range from about 622 MHz to 10 GHz. NPN transistors provided by this process have f of about 25GHz T value. Additionally, commercially available 0.13-0.25 μm CMOS processes with sufficiently fast transistors can be applied in some embodiments of the present invention, for example in circuits operating at low system frequencies.

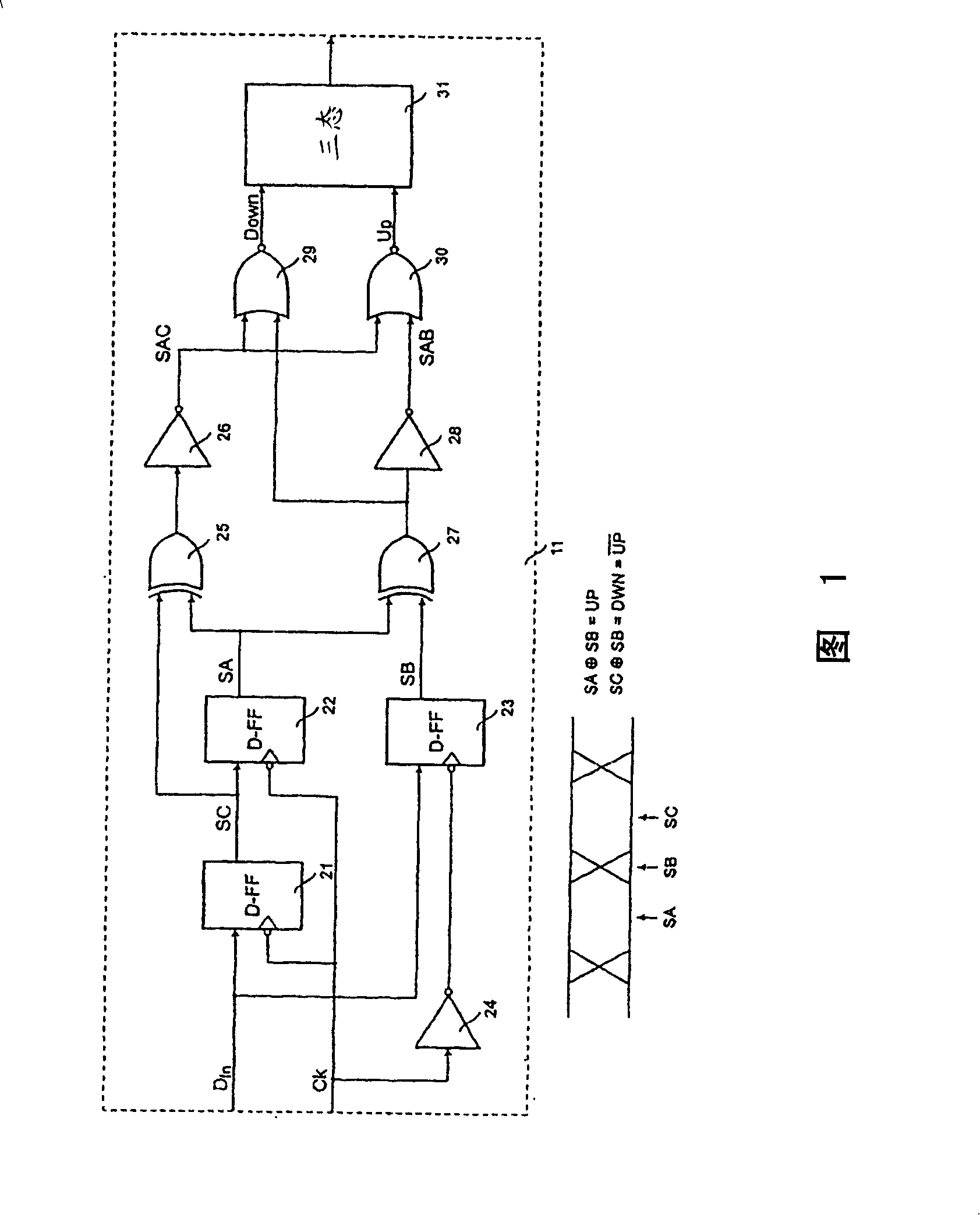

[0029] The basic operation of the pulse phase detector will be explained with reference to FIG. 1 , which shows an example of a pulse phase detector 11 . The phase detector 11 compares the clock signal C k and data signal D in A binary output signal is provided in response to a ph...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com