Semiconductor wafer package and its packaging method

A chip package, packaging method technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device parts and other directions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0148] Before the present invention is described in detail, it should be noted that throughout the description, the same elements are designated by the same reference numerals.

[0149] 1 to 10 show the first preferred embodiment of the packaging method of the semiconductor chip package of the present invention.

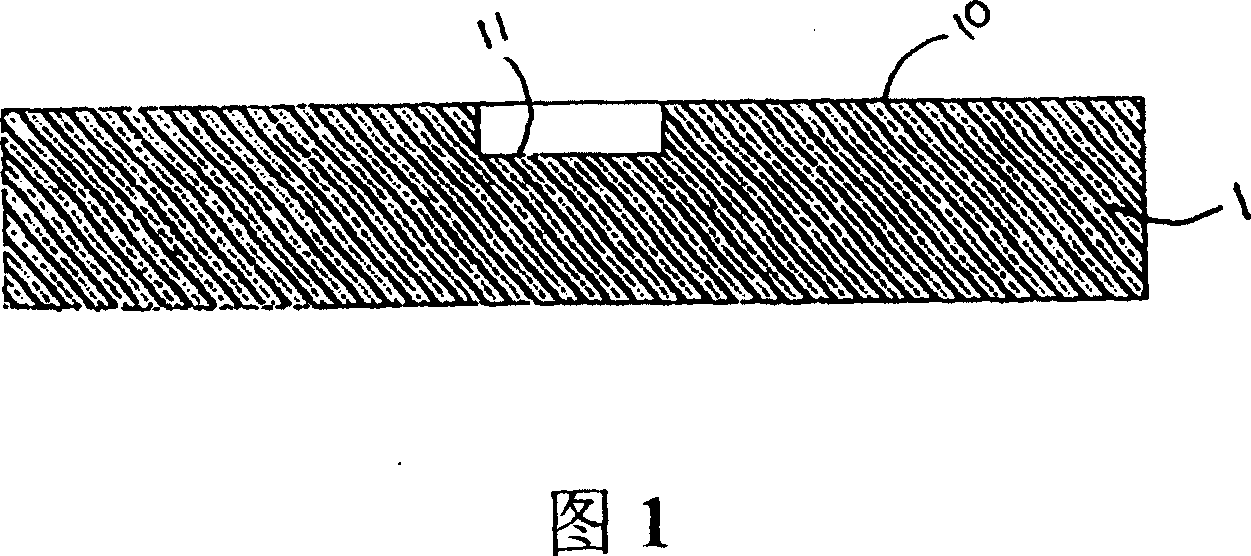

[0150] Referring to FIG. 1 in conjunction with FIG. 45, a semiconductor wafer 1 is first provided. The semiconductor wafer 1 has a bonding pad mounting surface 10 and a plurality of bonding pads 11 mounted on the bonding pad mounting surface 10 (in the drawings, only one bonding pad 11 is shown).

[0151] It should be noted that the semiconductor wafer 1 shown in FIG. 1 may be a single wafer that has been diced from the wafer, but may also be a wafer that has not been diced from the wafer.

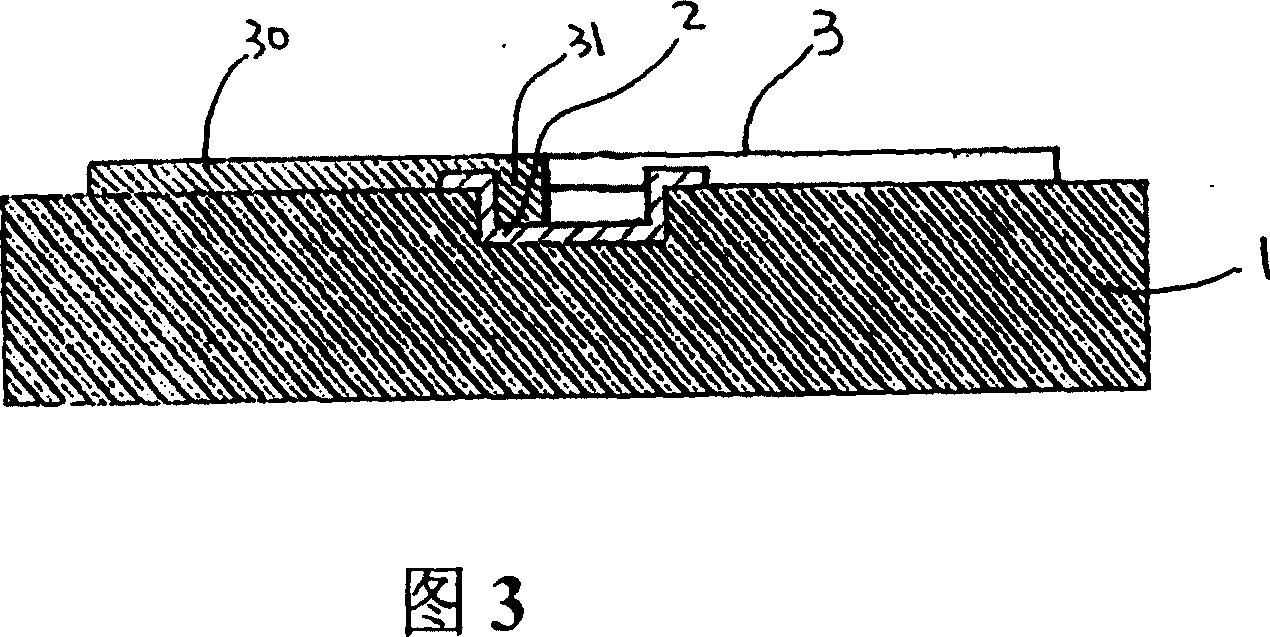

[0152] Next, as shown in FIG. 2 , a plating layer 2 is formed on each pad 11 of the chip 1 . The plating layer 2 will extend slightly onto the pad mounting surface 10 of the wa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com