Dynamic wordline assist scheme to improve performance tradeoff in SRAM

a dynamic and wordline technology, applied in static storage, information storage, digital storage, etc., can solve the problem of high area efficiency and high cost of away from the 6t cell, and achieve the effect of improving the tradeo

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

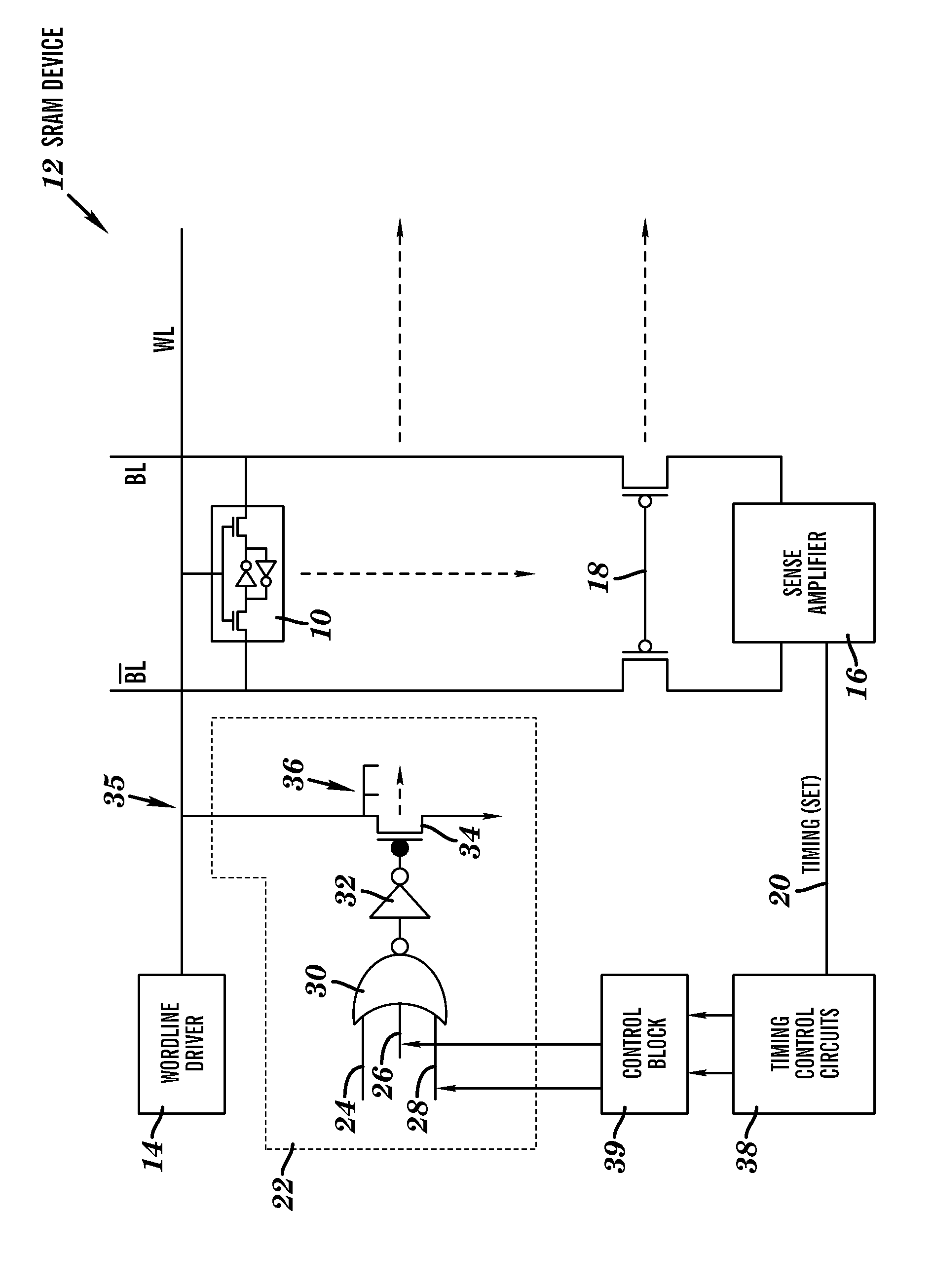

[0014]FIG. 1 depicts an illustrative 6T SRAM cell 10. Operations of such cells are well understood in the art and therefore are not described in detail. In general, a write operation occurs by placing opposite values on the bit lines, and asserting the wordline WL, which causes the values to be stored in the cell. A read operation generally includes precharging both bitlines to a logical 1, then asserting the word line WL. A sense amplifier coupled to the bit lines evaluates the result.

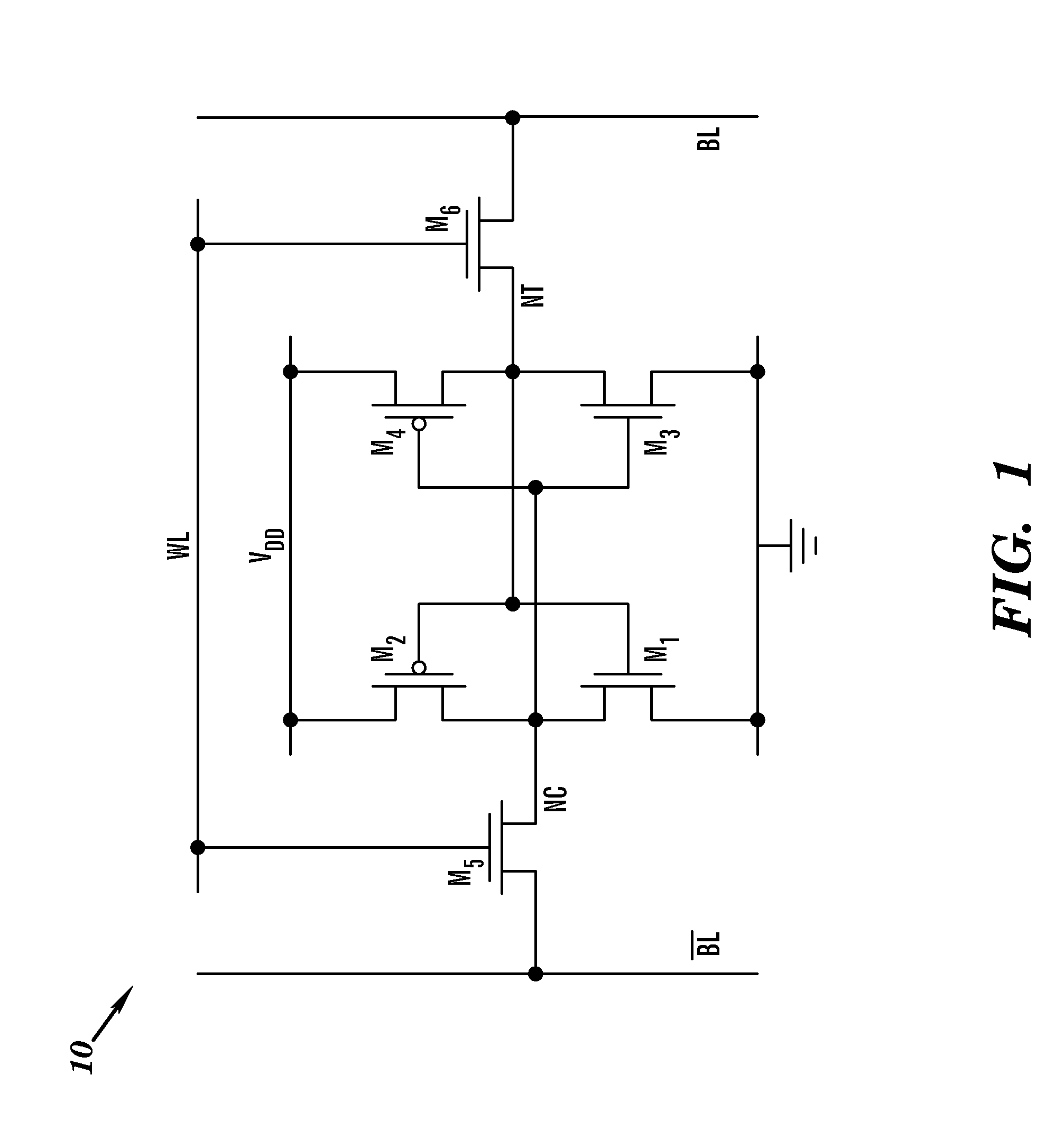

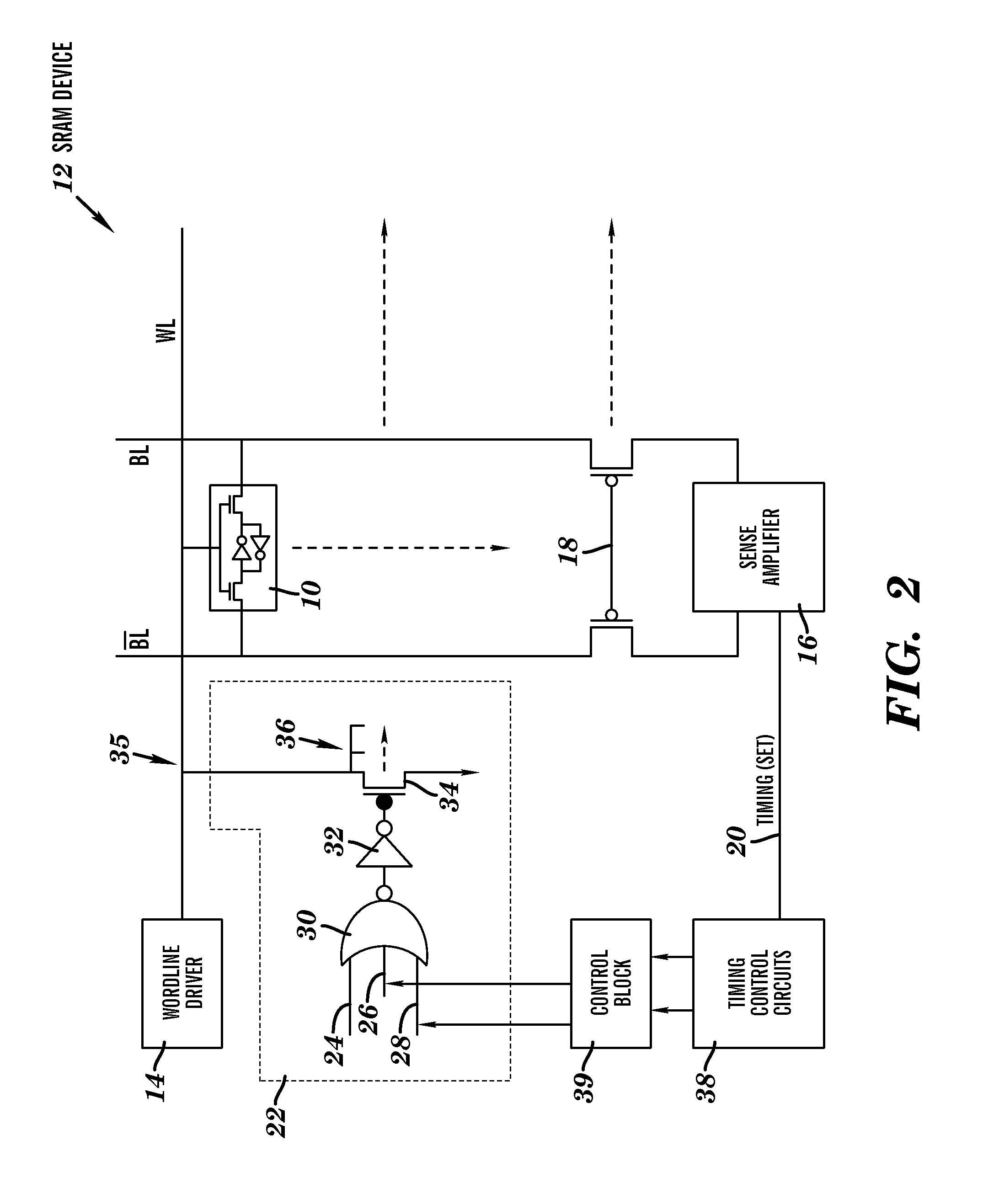

[0015]As noted, there tends to be a performance conflict between stability and readability / writeability in such cells. Techniques are known to increase stability, which has the adverse affect of decreasing readability / writeability. Similarly, techniques are known to increase readability / writeability, which has the adverse effect of decreasing stability. The present approach utilizes a dynamic assist circuit coupled to the wordline WL to achieve both improved stability and readability / writeability. In ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com