Integrated circuit

a technology of integrated circuits and diodes, applied in the direction of diodes, basic electric elements, semiconductor devices, etc., can solve the problems of insufficient esd robustness and attenuation of high-frequency signals supplied to rf input pads, and achieve the effects of reducing parasitic resistance, reducing esd robustness, and restrainting a diode siz

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029]The following describes the invention with reference to the accompanying drawings showing embodiments.

[0030]

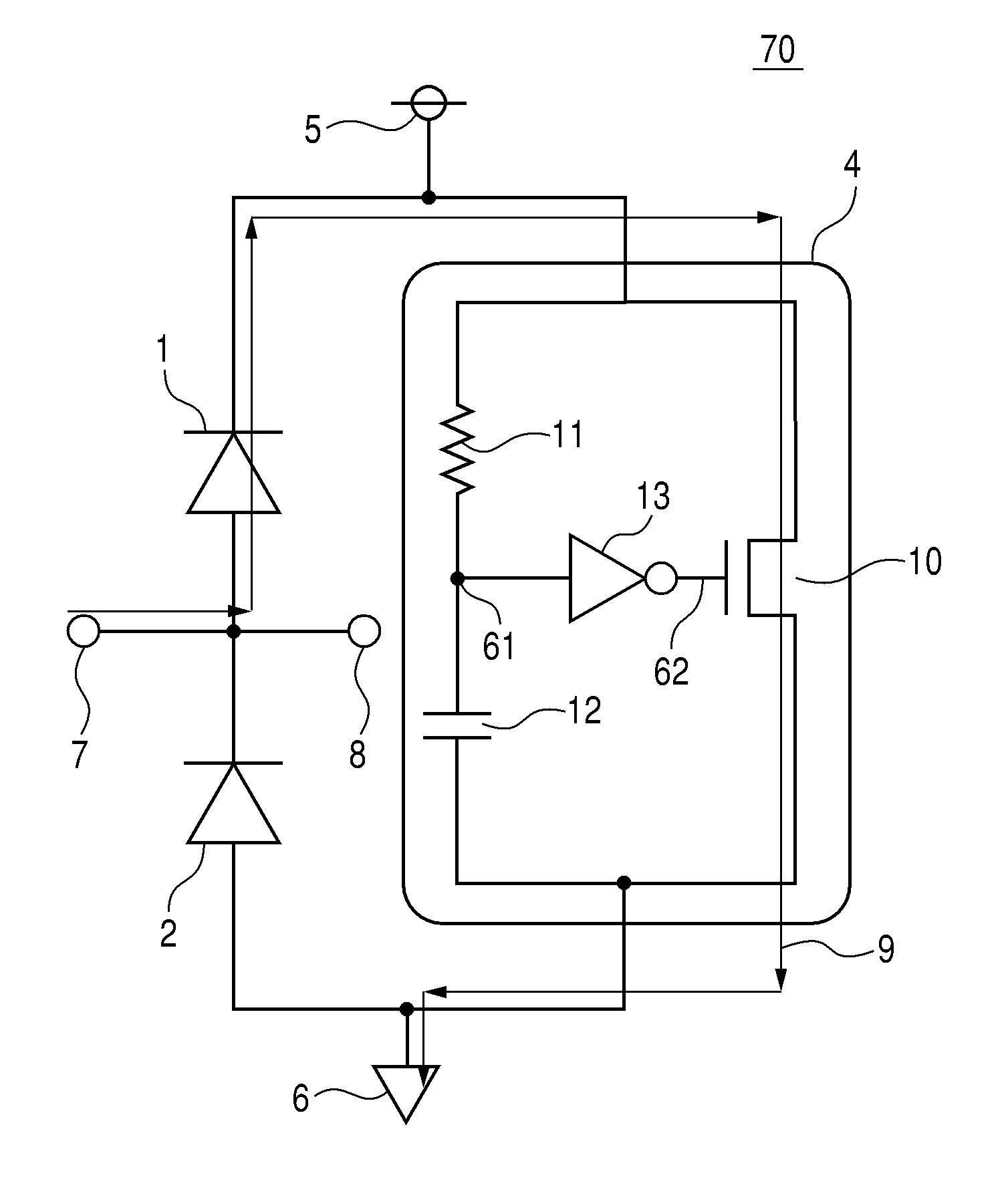

[0031]FIG. 5 shows a circuit diagram of the input protection circuit cell according to an embodiment of the invention.

[0032]An input protection circuit cell 70 is located between a signal pin of a mounted integrated circuit and an internal circuit including a high-frequency circuit. The input protection circuit cell 70 includes an input terminal 7 and an output terminal 8. The input terminal 7 is coupled to the signal pin. The output terminal 8 is coupled to the high-frequency circuit as well as the input terminal 7 and a node (coupling node) 60. A first diode 1 is provided between the node 60 and a high-voltage power supply (VDD) 5 and supplies an electric current from the node 60 to the VDD 5. A second diode 2 is provided between the node 60 and a low-voltage power supply (GND) 6 and supplies an electric current from the GND 6 to the node 60. Further, a clamp circuit 4...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com