Circuit substrate and circuit substrate manufacturing method

a manufacturing method and circuit substrate technology, applied in the direction of final product manufacturing, sustainable manufacturing/processing, semiconductor/solid-state device details, etc., can solve the problems of poor connection between circuit substrate and ic, difficult to accurately mount the ic on the circuit substrate, and heat damage to the circuit substra

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

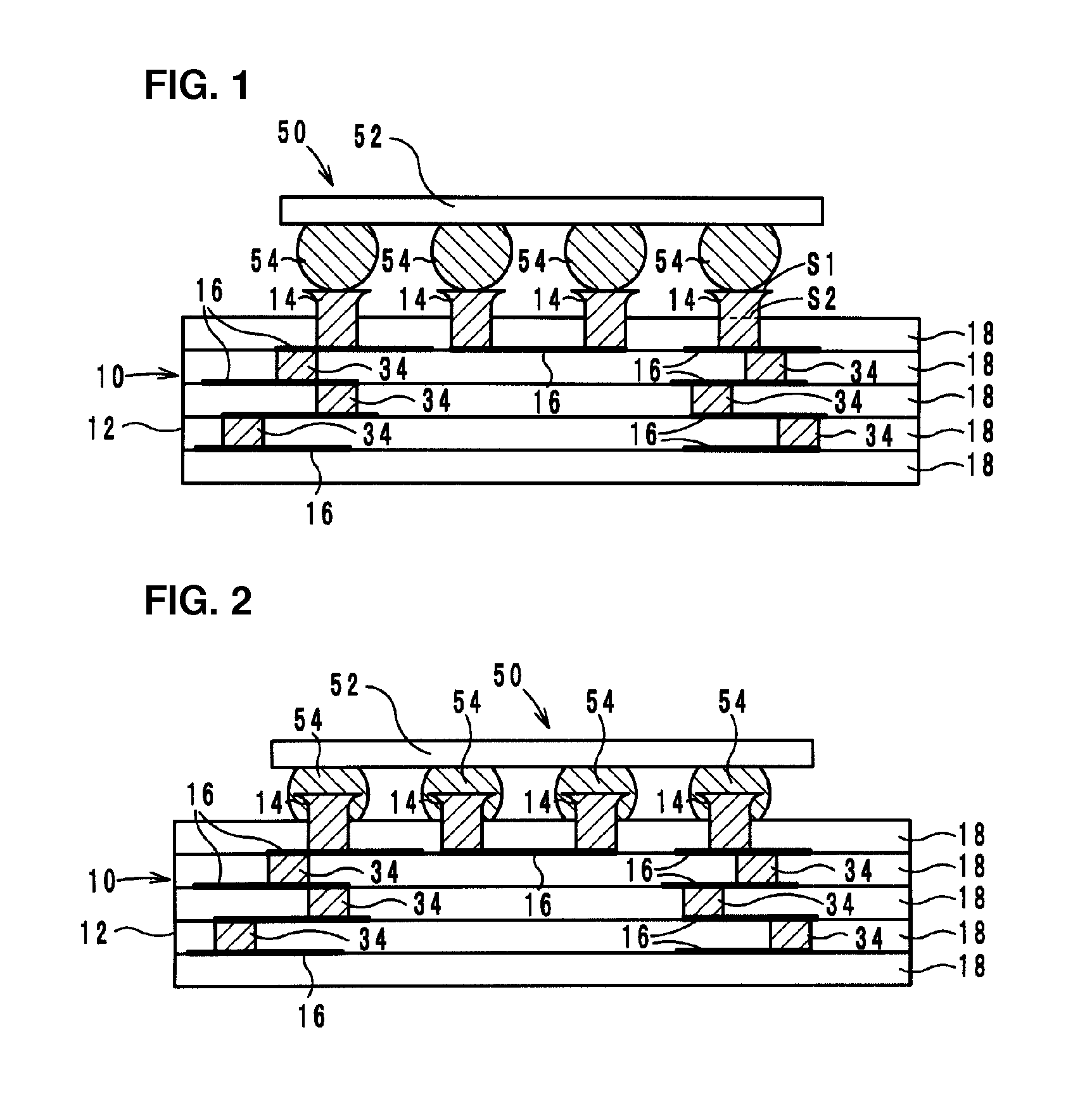

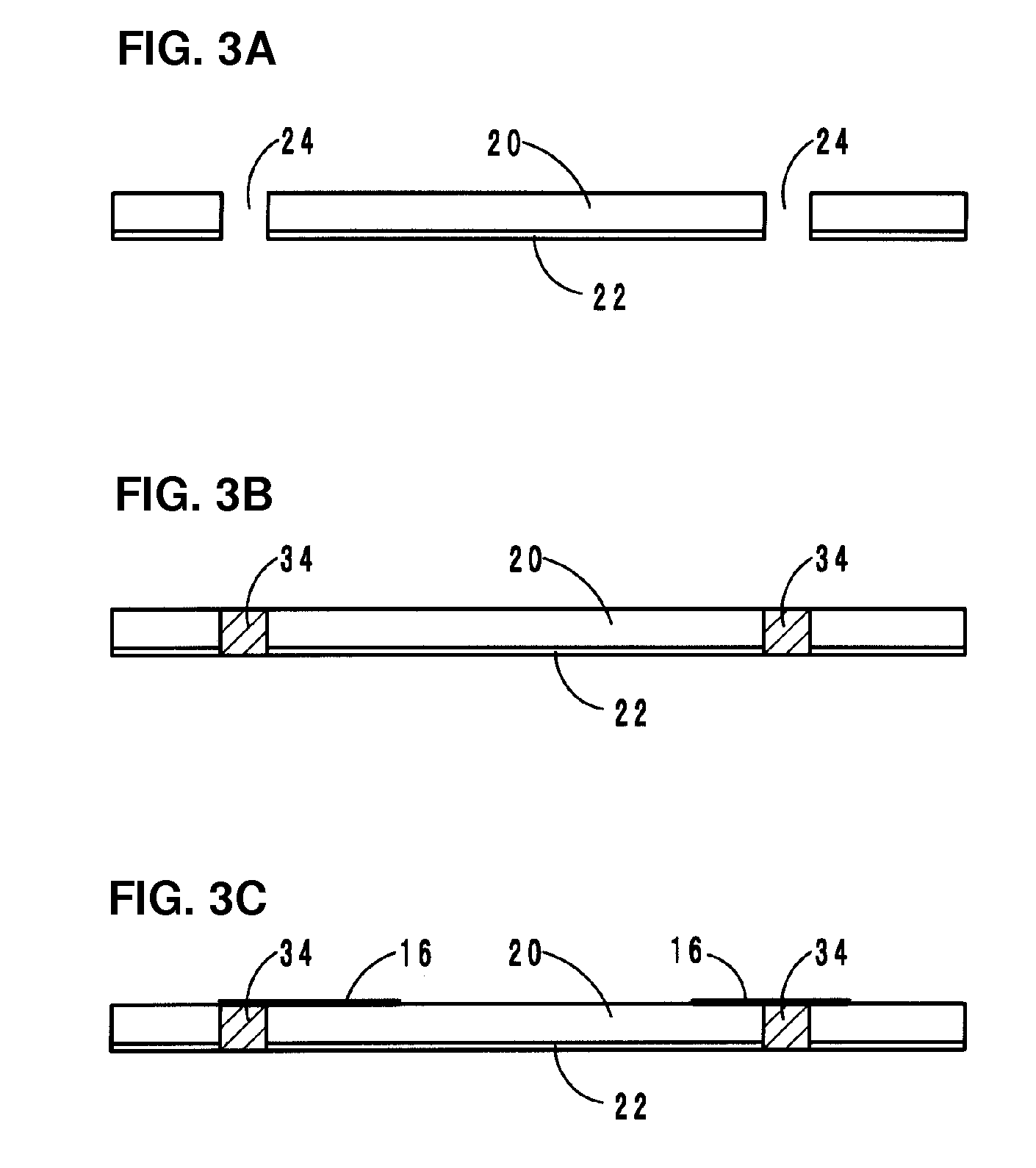

[0037]A configuration of a circuit substrate will be described below with reference to the drawings. FIG. 1 is a sectional structure drawing showing a state where a semiconductor integrated circuit (hereafter referred to as an “IC”) 50 is aligned with a circuit substrate 10. FIG. 2 is a drawing showing a sectional structure after reflow is performed on the IC 50 and circuit substrate 10 shown in FIG. 1.

[0038]The circuit substrate 10 is a substrate on which the IC 50, which is an electronic component, is to be surface-mounted. As shown in FIG. 1, the circuit substrate 10 includes a substrate body 12, terminal 14, and internal conductive layers 16. The substrate body 12 is preferably formed by laminating multiple ceramic layers 18, which are insulators. The internal conductive layers 16 are laminated together with the ceramic layers 18 inside the substrate body 12 so as to form a circuit. The internal conductive layers 16 are connected to one another through via conductors 34.

[0039]Th...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Temperature | aaaaa | aaaaa |

| Temperature | aaaaa | aaaaa |

| Temperature | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com