Methods of forming vertical transistors

a transistor and vertical technology, applied in transistors, semiconductor devices, electrical equipment, etc., can solve the problems of doubt regarding the possibility of achieving the desired progress of the standard one transistor/one capacitor cell design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015]Observation and study indicates that vertical transistors configured to exhibit a floating body effect show promise as a device allowing improvements in data access speed and reduced power consumption while further providing a reduced number of photomasks. While not being limited to use in memory devices, such vertical transistors may allow scaling not otherwise obtainable with the standard one transistor / one capacitor cell design of conventional memory devices, for example, DRAM.

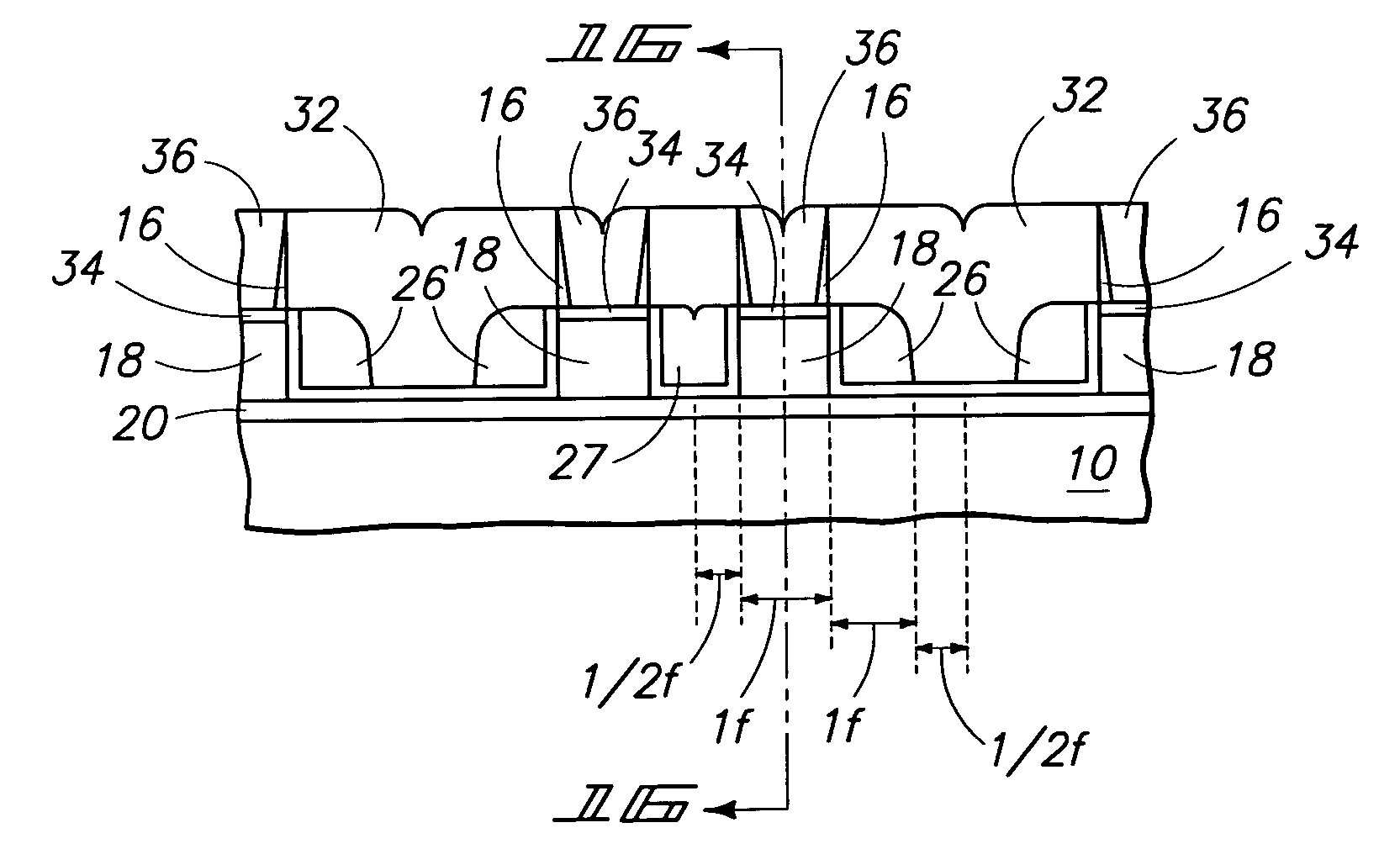

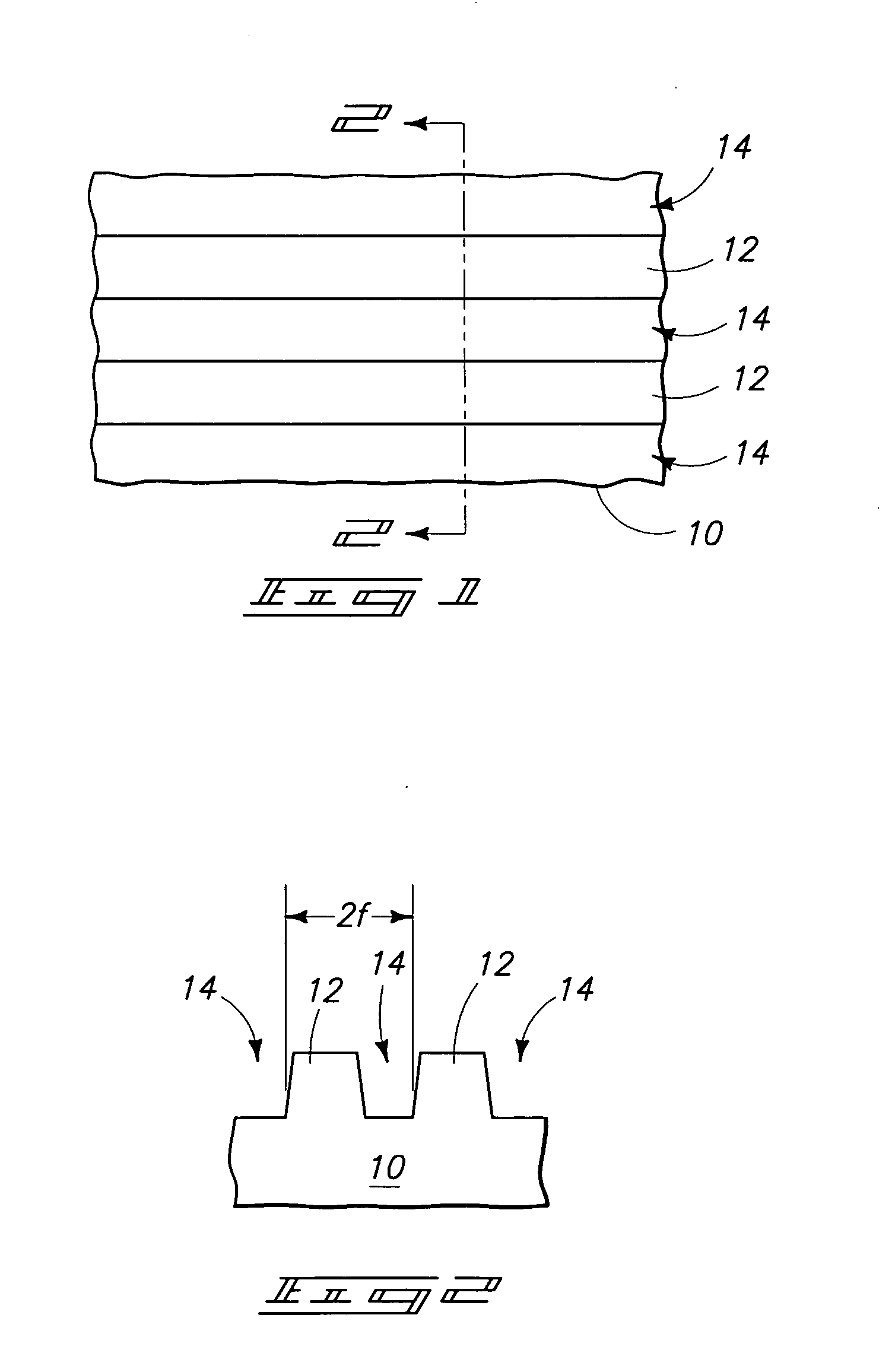

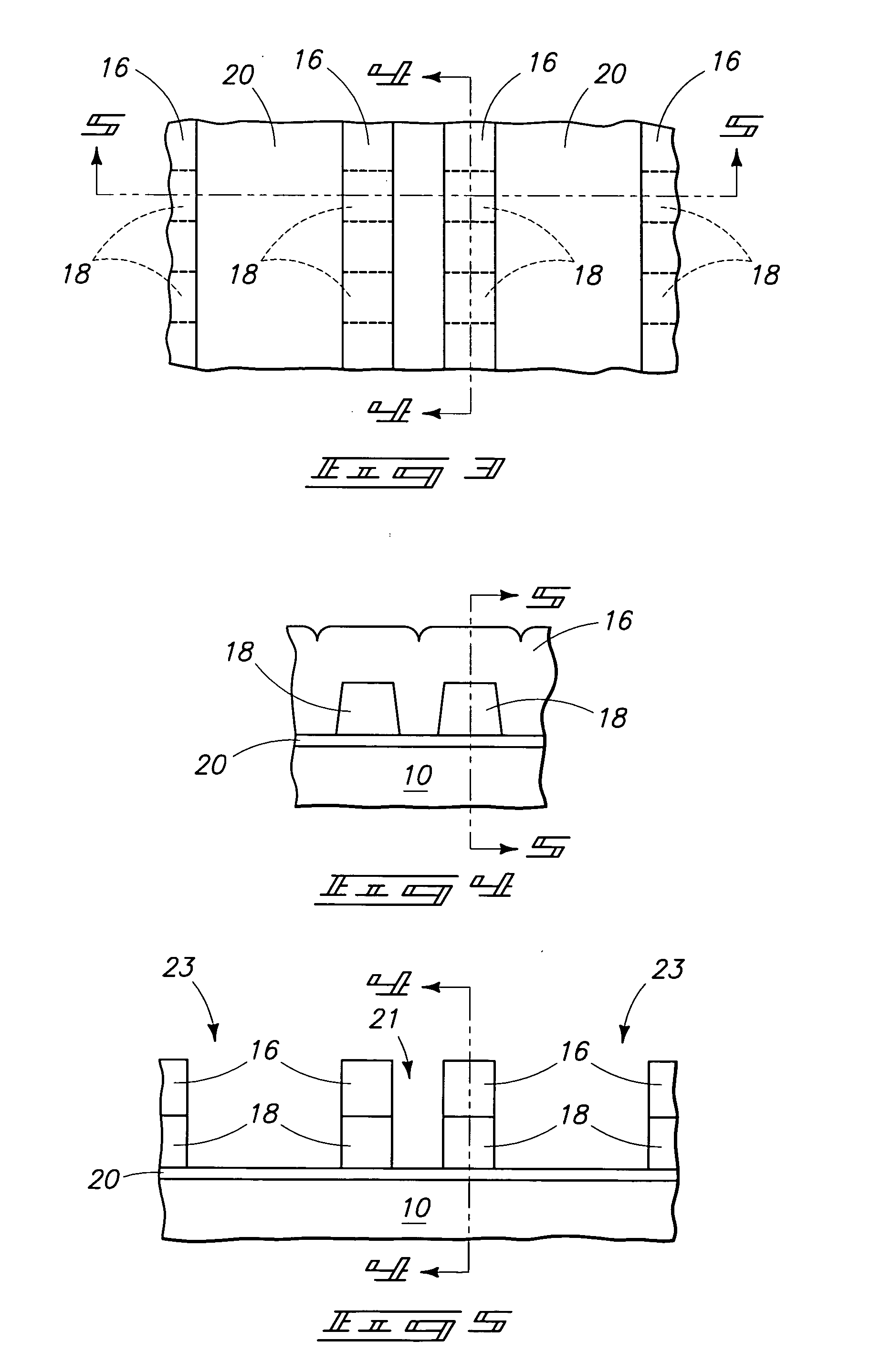

[0016]According to one embodiment of the invention, a vertical transistor forming method includes forming a first semiconductive pillar elevationally above a first transistor source / drain in a semiconductive substrate and laterally between a second semiconductive pillar and a third semiconductive pillar. The first pillar is closer to the second pillar than to the third pillar, thus, providing a first recess between the first and second pillars and a wider second recess between the first and third pill...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com