Flexible Microprocessor Register File

a microprocessor and register file technology, applied in the field of programmable circuits, can solve the problems of obviating the benefits of using a vector, difficult to apply stall conditions for instructions that use indirect access, and register may not be known

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019]The numerous innovative teachings of the present application will be described with particular reference to the presently preferred embodiment (by way of example, and not of limitation).

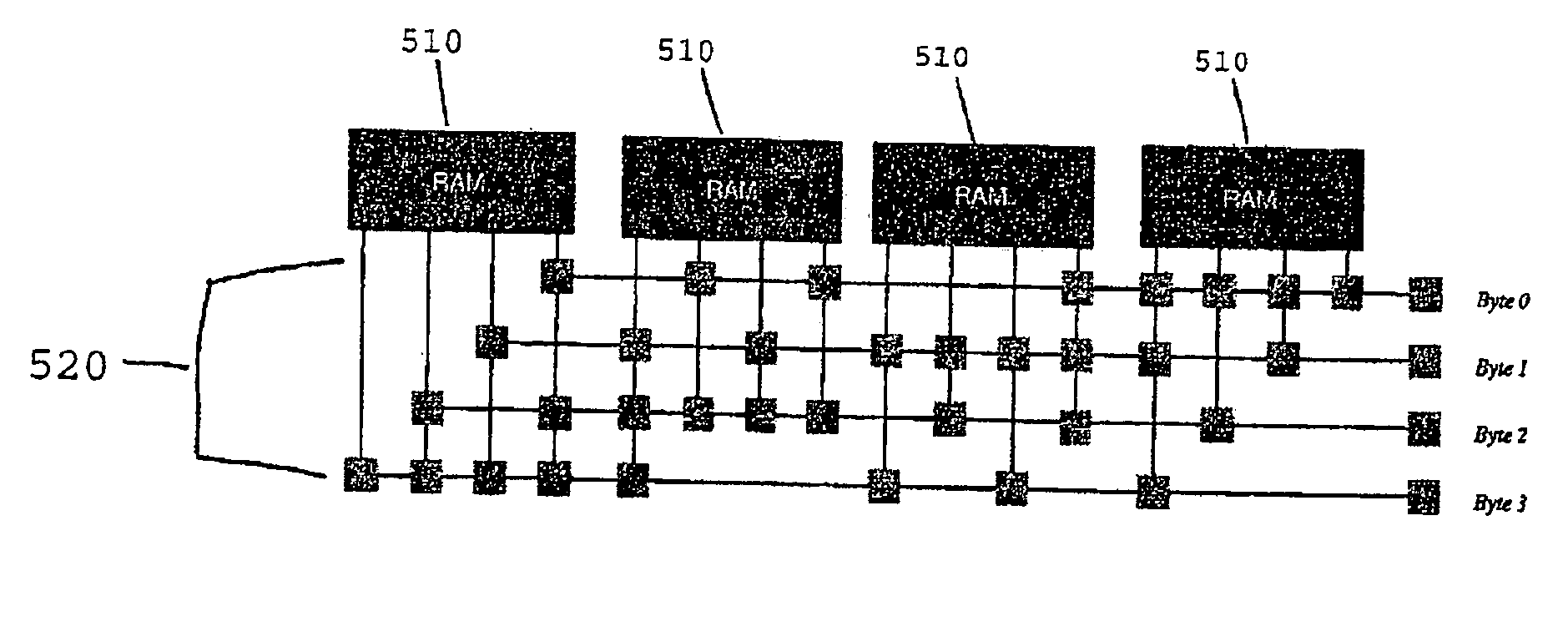

Transposable Register-File Operation

[0020]The transposable register-file is a novel microprocessor register-file data organization scheme which overcomes many of the disadvantages of traditional data organization in microprocessor register-file, and which has the benefits of allowing a microprocessor register-file to be viewed in multiple formats with a reduction of the number of program instructions required during byte, word and long word data reformatting. The preferred embodiment supports both byte-transpose and word-transpose.

[0021]Byte-Transpose Register File

[0022]FIG. 1 shows how four consecutive registers are viewed with byte-transpose enabled. With reference to FIG. 1, left hand side (110) illustrates those registers before transpose enabled. Each row in FIG. 1 represents one register ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com