Storage controller, data processing method and computer program product

a storage controller and data processing technology, applied in the field of storage controllers, data processing methods and computer program products, can solve the problems of ineffective utilization of the rest of the channel processor resources, and achieve the effects of reducing channel processor overhead, efficient cache slot management, and speeding up the fibre channel interfa

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] An embodiment of the present invention is described below with reference to the attached drawings.

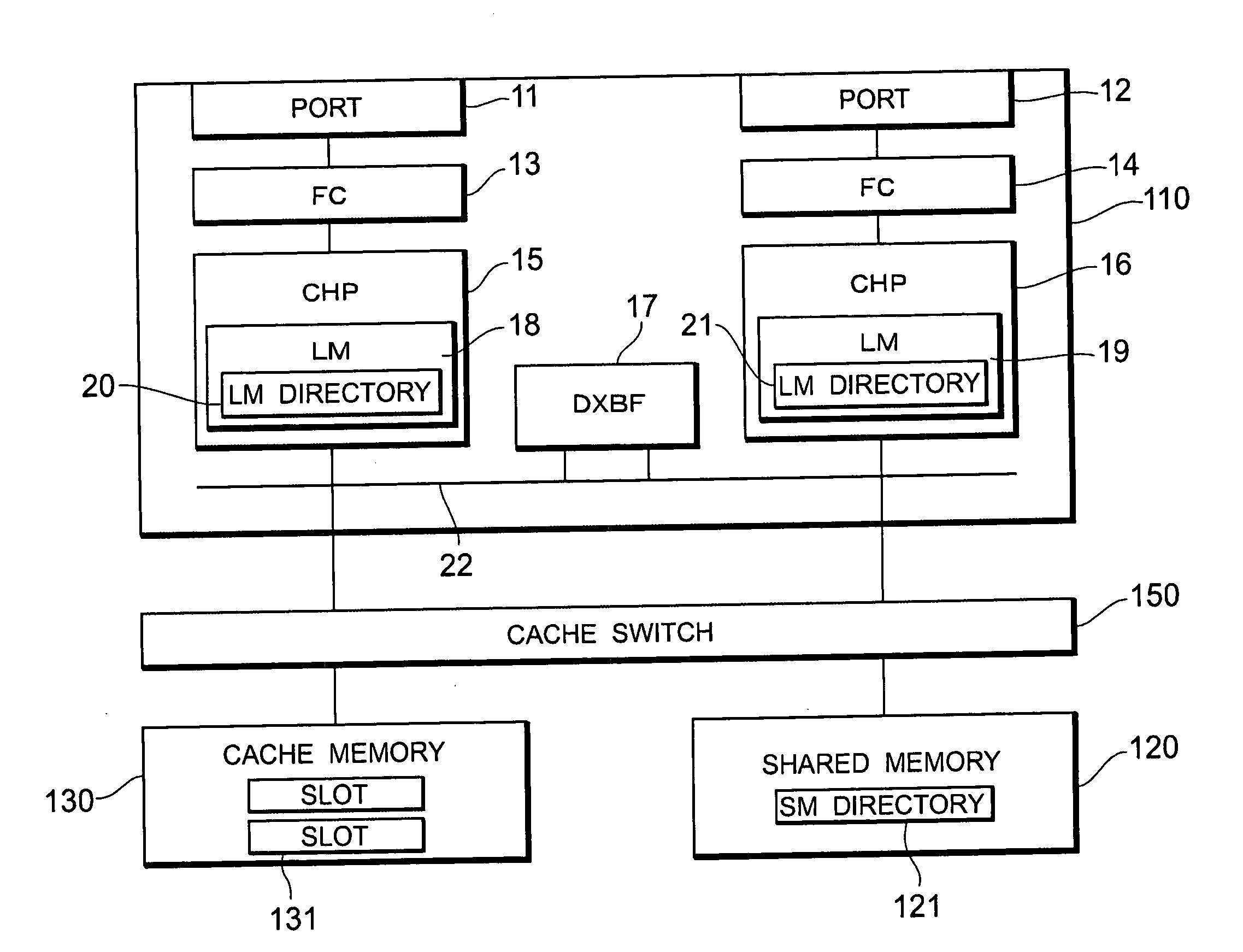

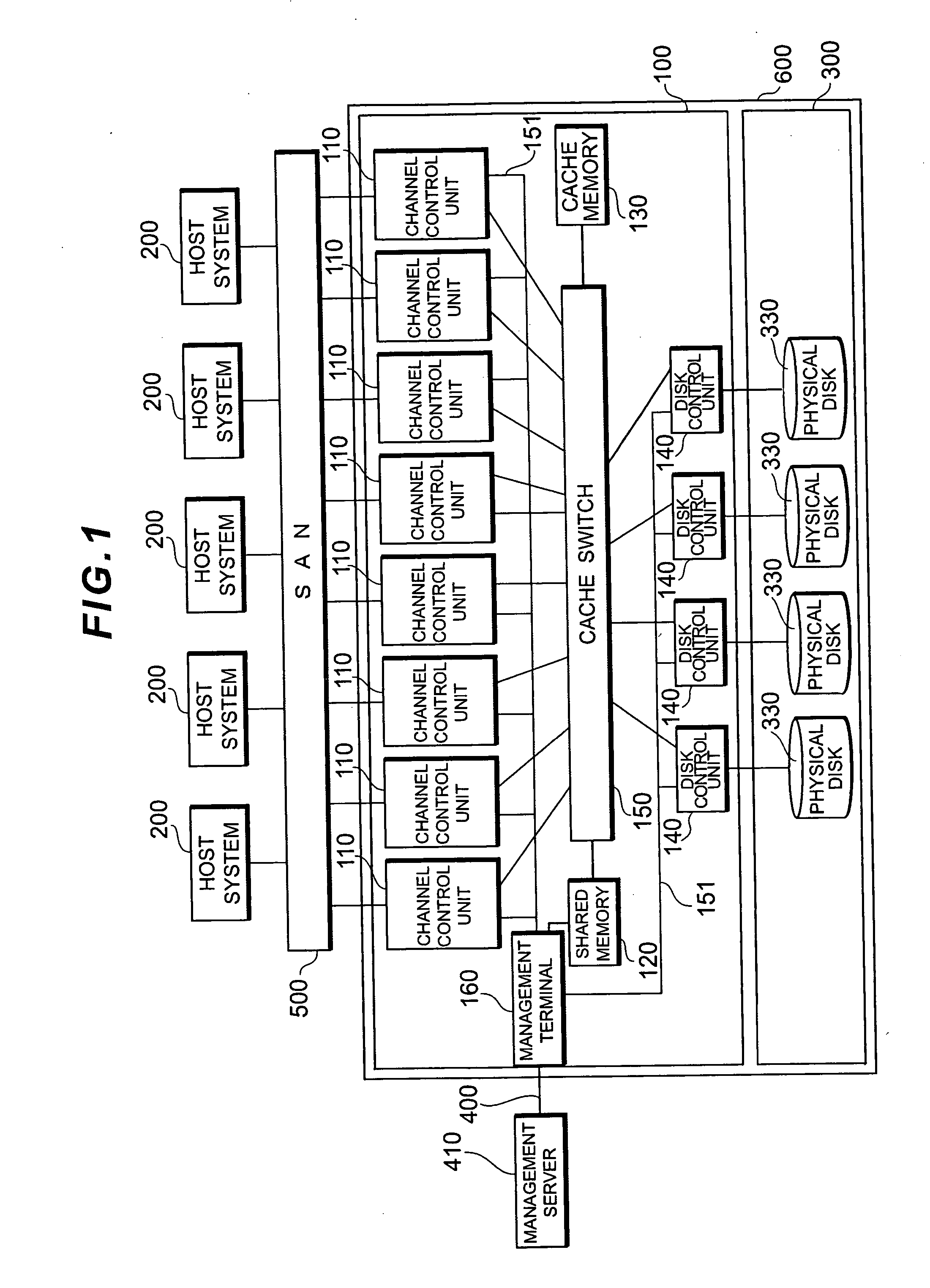

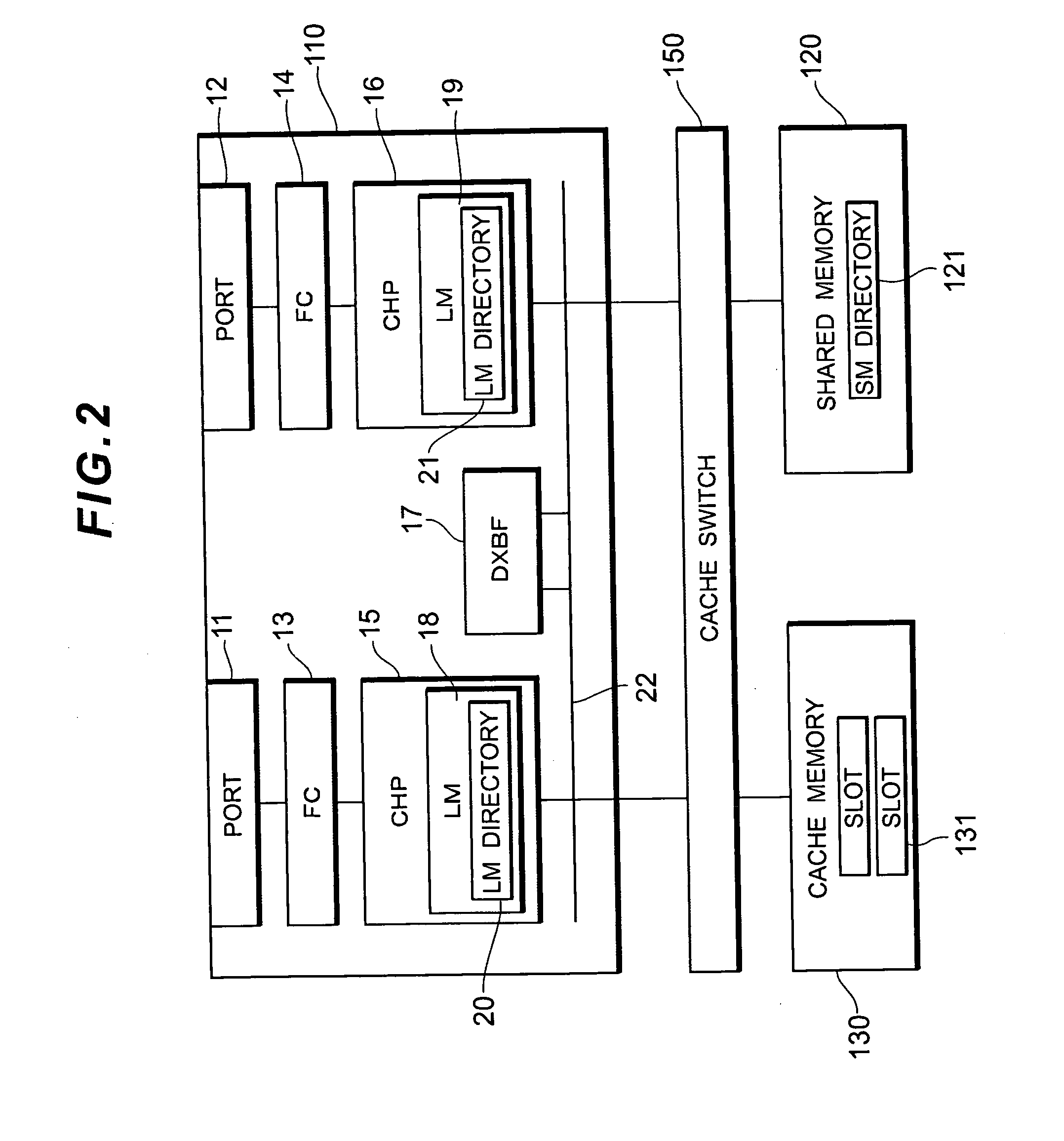

[0016]FIG. 1 shows the hardware structure of a storage system 600 according to the present embodiment. The storage system 600 is mainly composed of a storage controller 100 and a storage apparatus 300. The storage controller 100 controls data input and output to and from the storage apparatus 300 according to, for example, commands from host systems 200. It also performs various processing, such as setting and changing of structural information for the storage system 600 according to, for example, commands from a management server 410.

[0017] Host systems 200 are front-end computers such as personal computers, work stations, or mainframe computers, and are used as automated teller machines in banks or flight seat reservation systems. The host systems 200 are connected to the storage controller 100 via a SAN 500 to enable communication therebetween. The SAN 500 is a network for t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com