Line level air gaps

a microelectronic and integrated circuit technology, applied in the direction of electrical equipment, semiconductor devices, semiconductor/solid-state device details, etc., can solve the problems of increased intra-level interaction, increased energy consumption, and increased ic risk at line level, and achieve the effect of robust mechanical stability and the biggest impact on rc delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

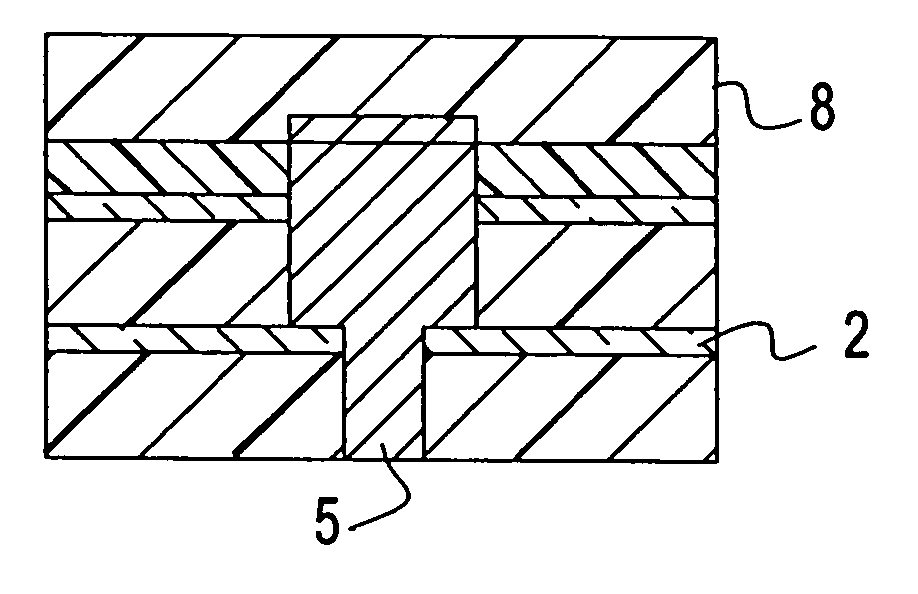

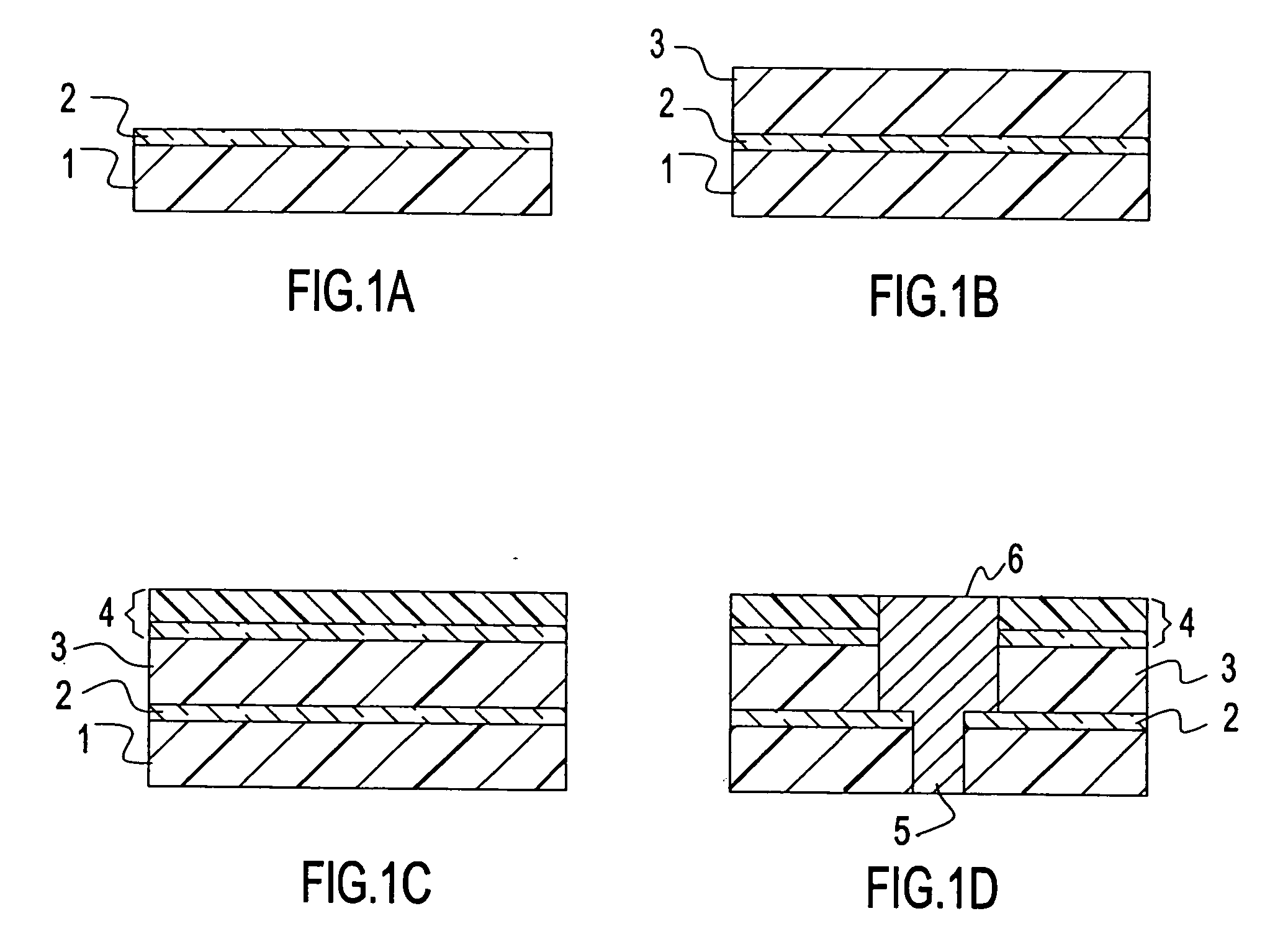

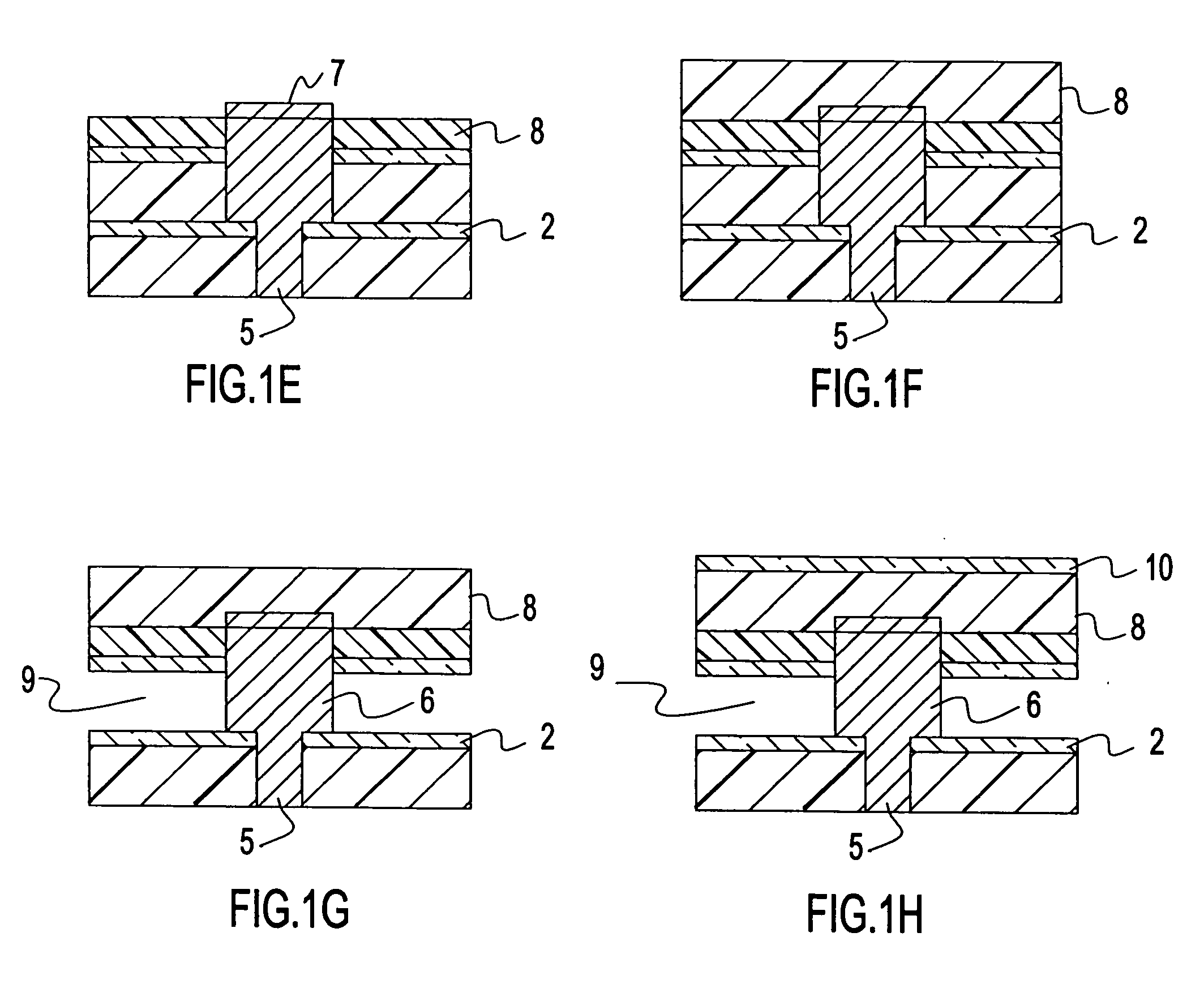

[0021]FIG. 1A shows the initial fabrication steps on the top surface of a semiconductor substrate (not shown) of an IC structure of the present invention. The first layer of a solid permanent ultra-low-K dielectric material 1 has been deposited on the substrate for patterning of the first via level. Examples of suitable porous and substantially non-porous gas permeable materials used to function as the solid permanent low-K dielectric at via levels include: porous SiLK and SiLK, a polymer product of Dow Chemical Company, which is applied as a spin-coated oligomeric solution and cured at about 400° C.-450° C.; porous SiCOH and SiCOH, a glassy spin-on material such as JSR, a product of JSR Micro; and methyl silsesquioxane (MSSQ). A first gas impermeable etch stop layer 2 has been deposited on the layer of permanent dielectric material 1 by means known in the art, such as spin-on, chemical vapor deposition (CVD) and the like. Examples of suitable materials used to function as the etch ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com