Semiconductor device and method of manufacturing the same

a semiconductor and semiconductor technology, applied in the direction of semiconductor devices, electrical equipment, transistors, etc., can solve the problems of difficult junction leakage reduction, many defects in the silicon nitride film that covers the side surfaces of the refractory metal film, etc., and achieve the effect of effectively preventing the scattering of refractory metal

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] Preferred embodiments of the present invention will now be described in detail with reference to the accompanying drawings.

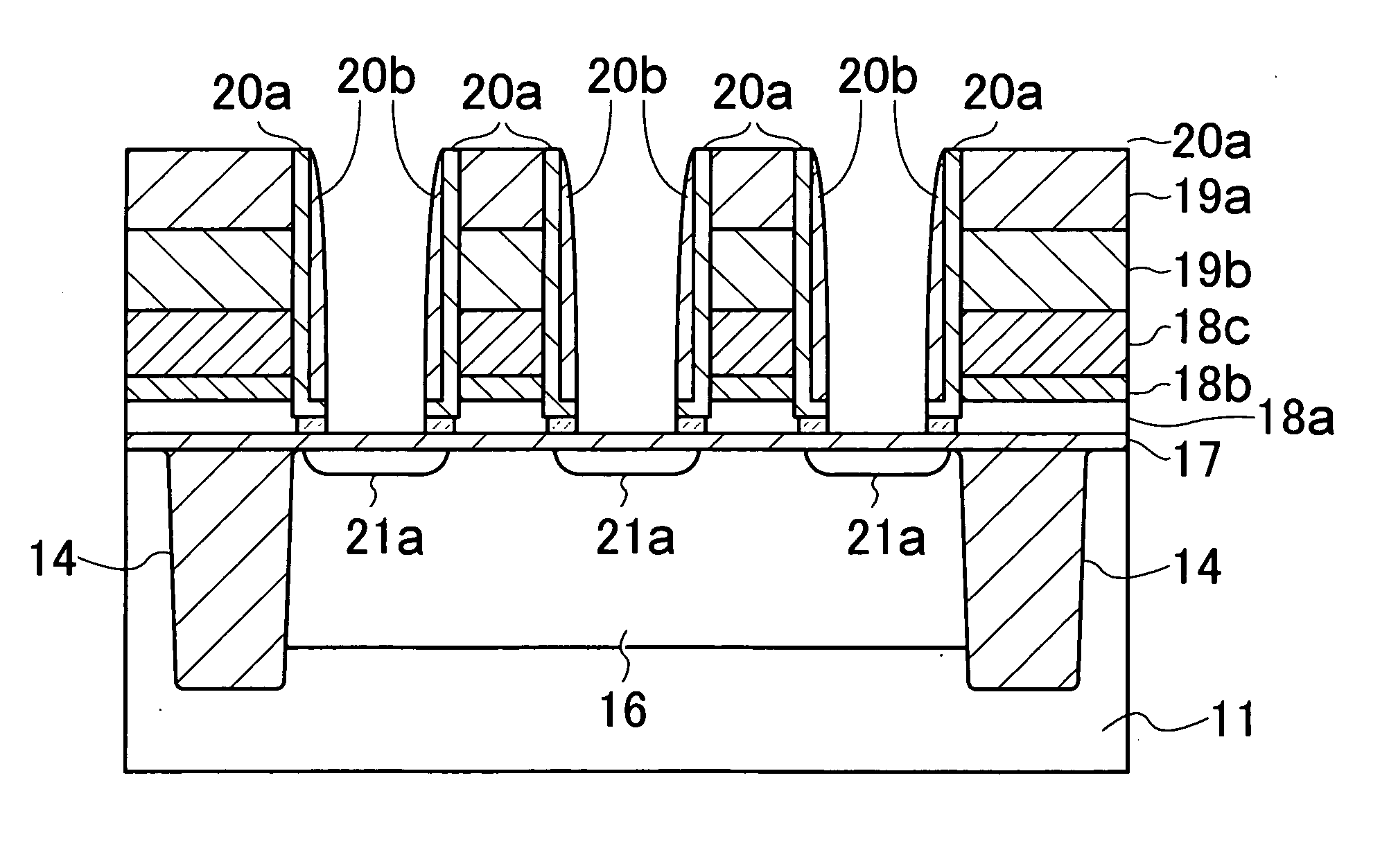

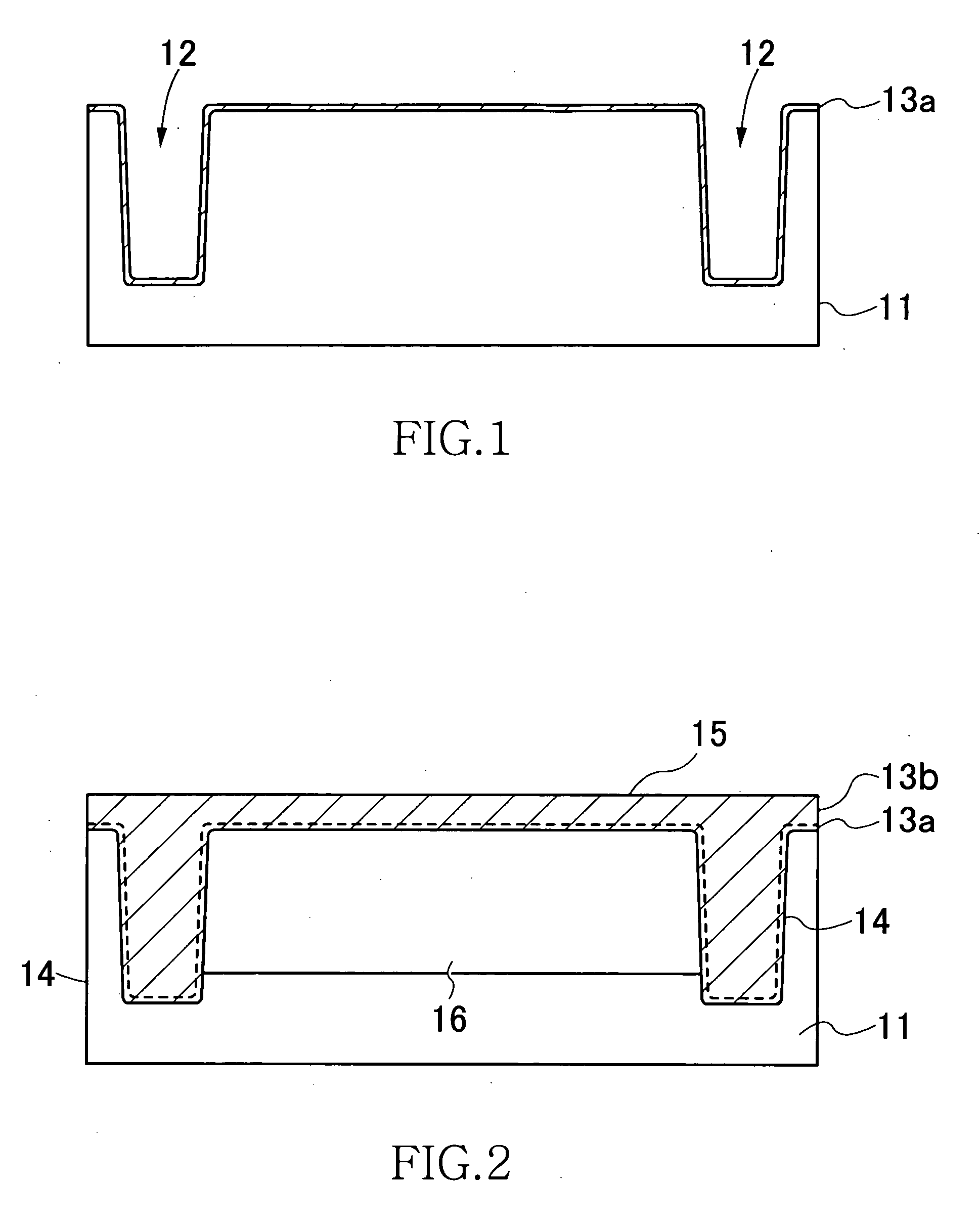

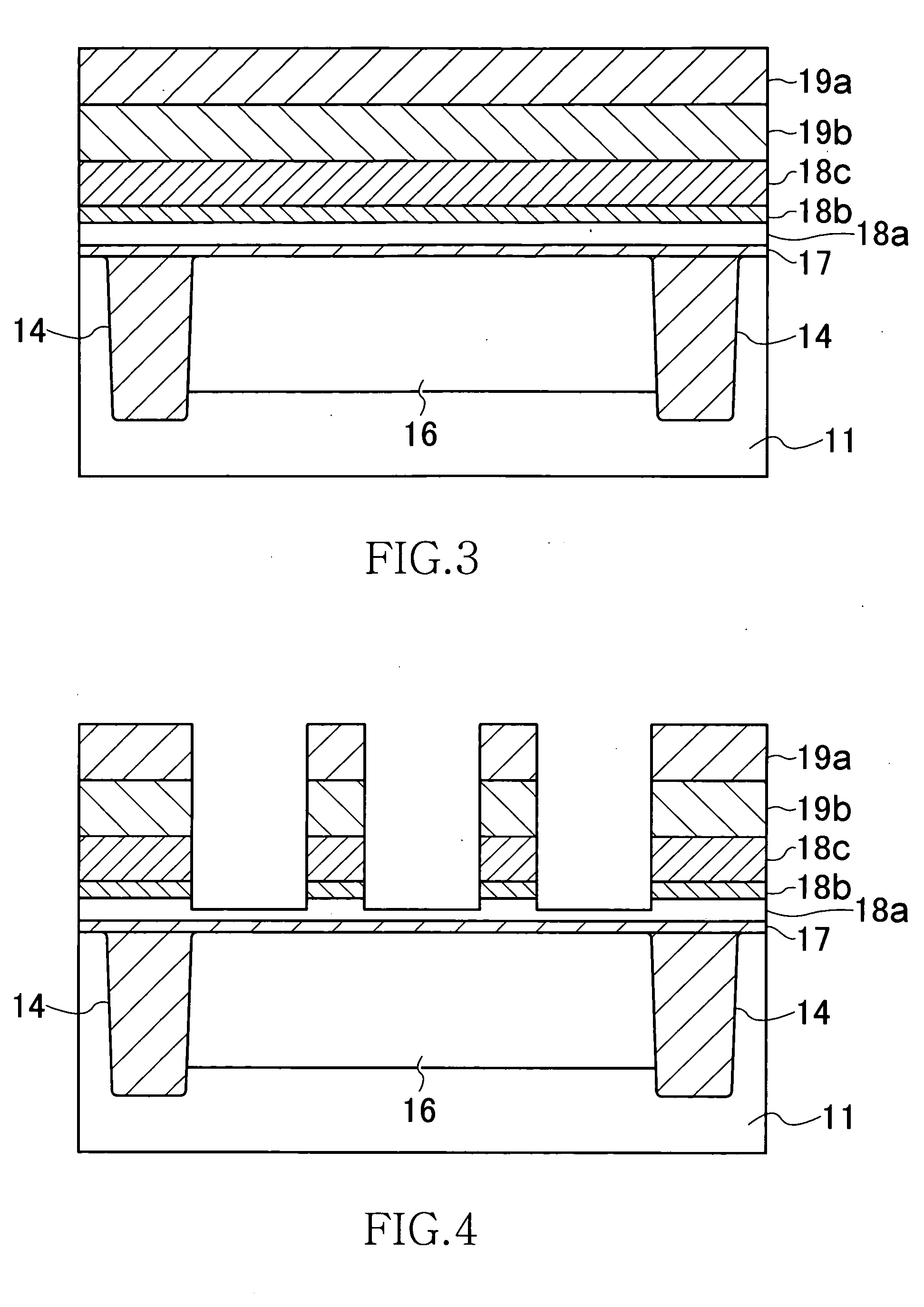

[0038]FIG. 1 to FIG. 21 is schematic cross sections of processes of a method of manufacturing a semiconductor device according to the exemplary embodiment of the present invention. In the present embodiment, the manufacturing method according to the present invention is applied to a DRAM.

[0039] First, as shown in FIG. 1, a semiconductor substrate 11 made of p-type mono-crystalline silicon having a specific resistance of about 1 to 10 Ω / cm is etched, thereby forming an element isolation trench 12 having a depth of about 350 nm. The semiconductor substrate 11 is thermally oxidized at about 1,000° C., thereby forming a silicon oxide film 13a as thin as about 10 nm on an inner wall of the element isolation trench 12. This silicon oxide film 13a is formed to repair a damage generated on the inner wall of the element isolation trench 12 due to the etching, an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com