Semiconductor fabrication and structure for field-effect and bipolar transistor devices

a technology of bipolar transistors and semiconductors, applied in the field of semiconductor devices, to achieve the effect of enhancing the properties of semiconductor devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] An n-type silicon wafer having an original bulk spreading resistivity of about 40 ohm-cm was implanted with 180 keV protons to a dose of about 3×1016 protons / cm2 and annealed in a nitrogen-hydrogen atmosphere at 900 degrees C. for 10 seconds to develop a buried hydrogen bubble or platelet layer, as further described in the Li patents. The implanted wafer was annealed by heating to 1180 degrees C. for 20 minutes for conversion of the top surface layer from n-type to p-type conductivity as further described in the 1996 MRS article. The surface of the annealed wafer was subjected to plasma etching to reduce the thickness of the top surface layer overlying the buried layer to approximately 0.1 μm. Other suitable means for thickness reduction include chemical etching and chemical-mechanical polishing (CMP).

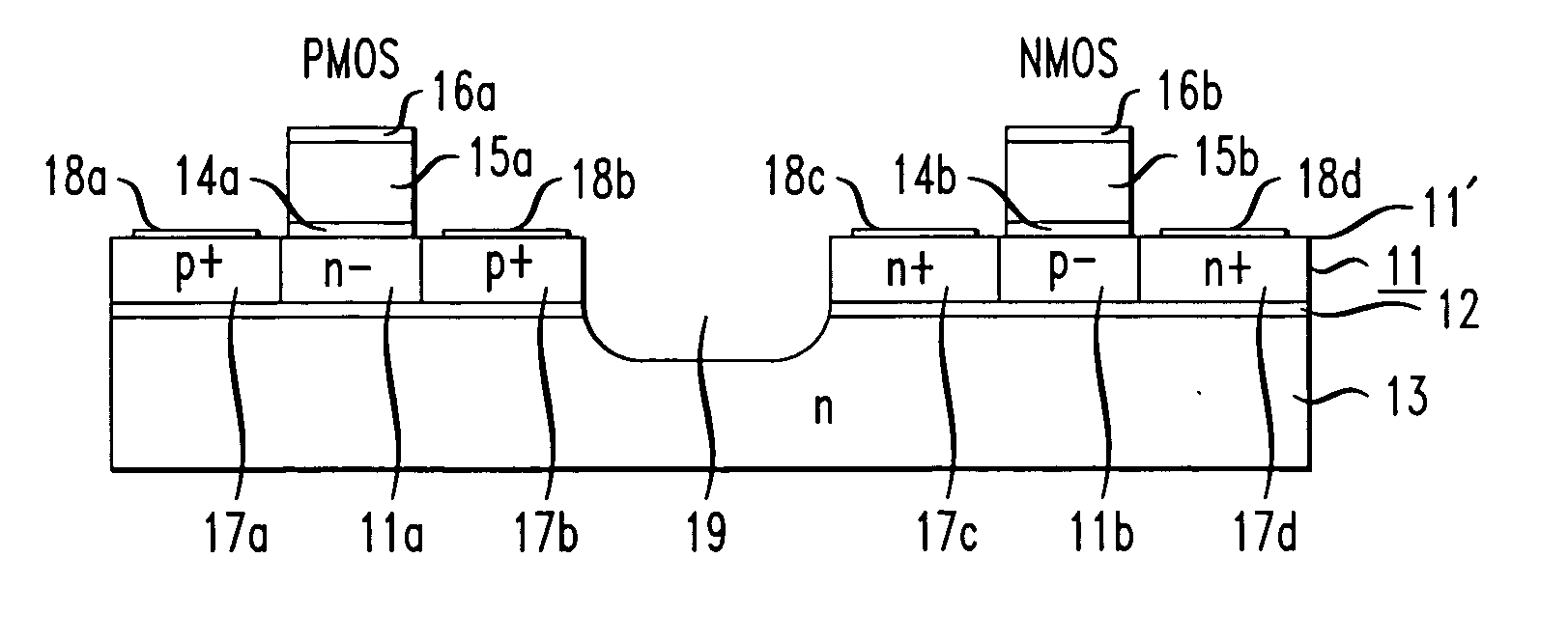

[0019] For the resulting structure, FIG. 1 shows spreading resistivity versus depth as measured from the surface of the reduced-thickness surface layer. As compared with the sp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com