Method for direct attachment of a chip to a cooling member

a cooling member and chip technology, applied in the direction of adhesive processes, layered products, chemical instruments and processes, etc., can solve the problems of irrecoverable module yield loss, insufficient process improvement alone to eliminate all the problems affecting both performance and reliability, and insufficient heat flow, etc., to achieve steady state operation of the semiconductor chip, the effect of sufficient bond strength

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

)

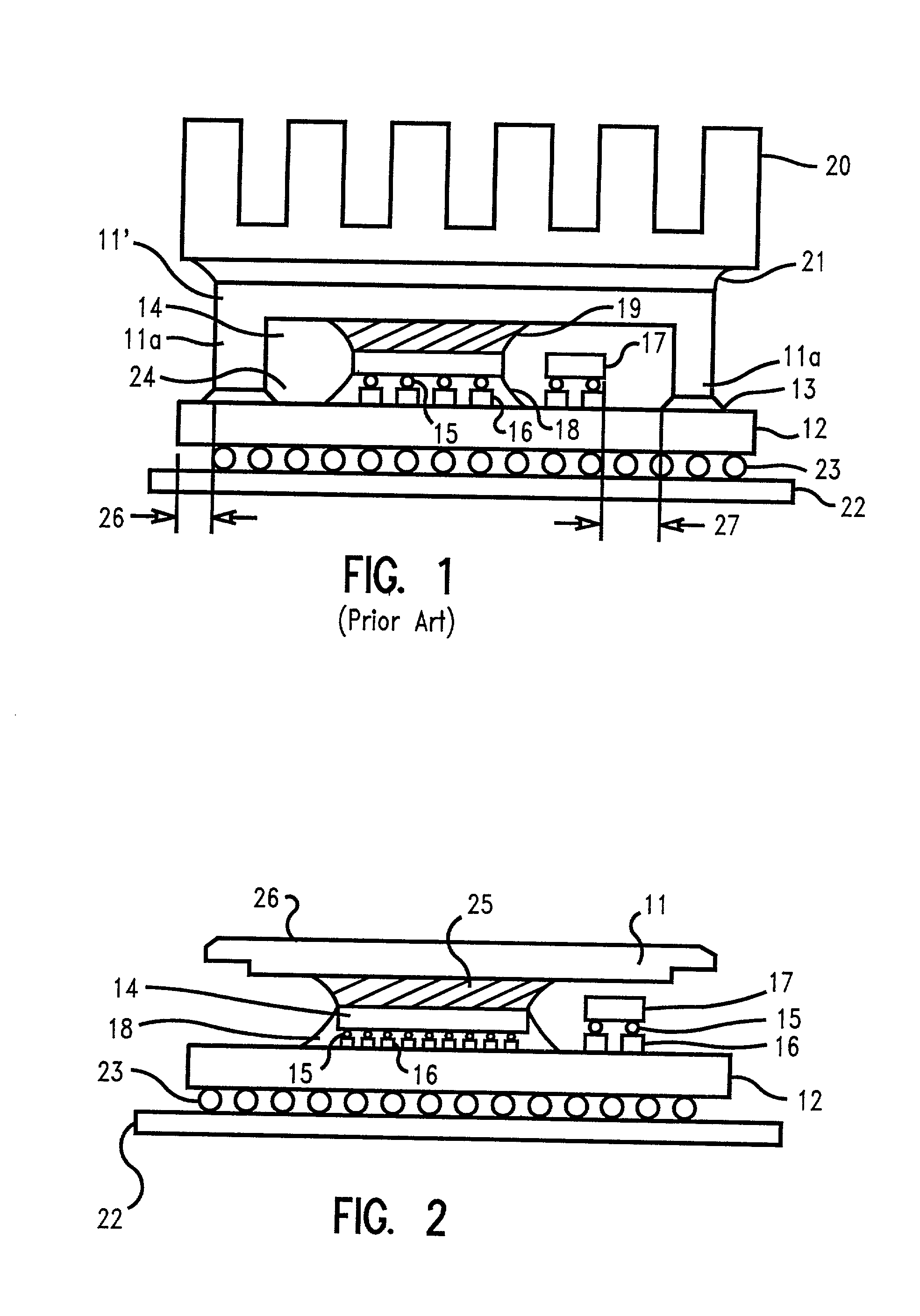

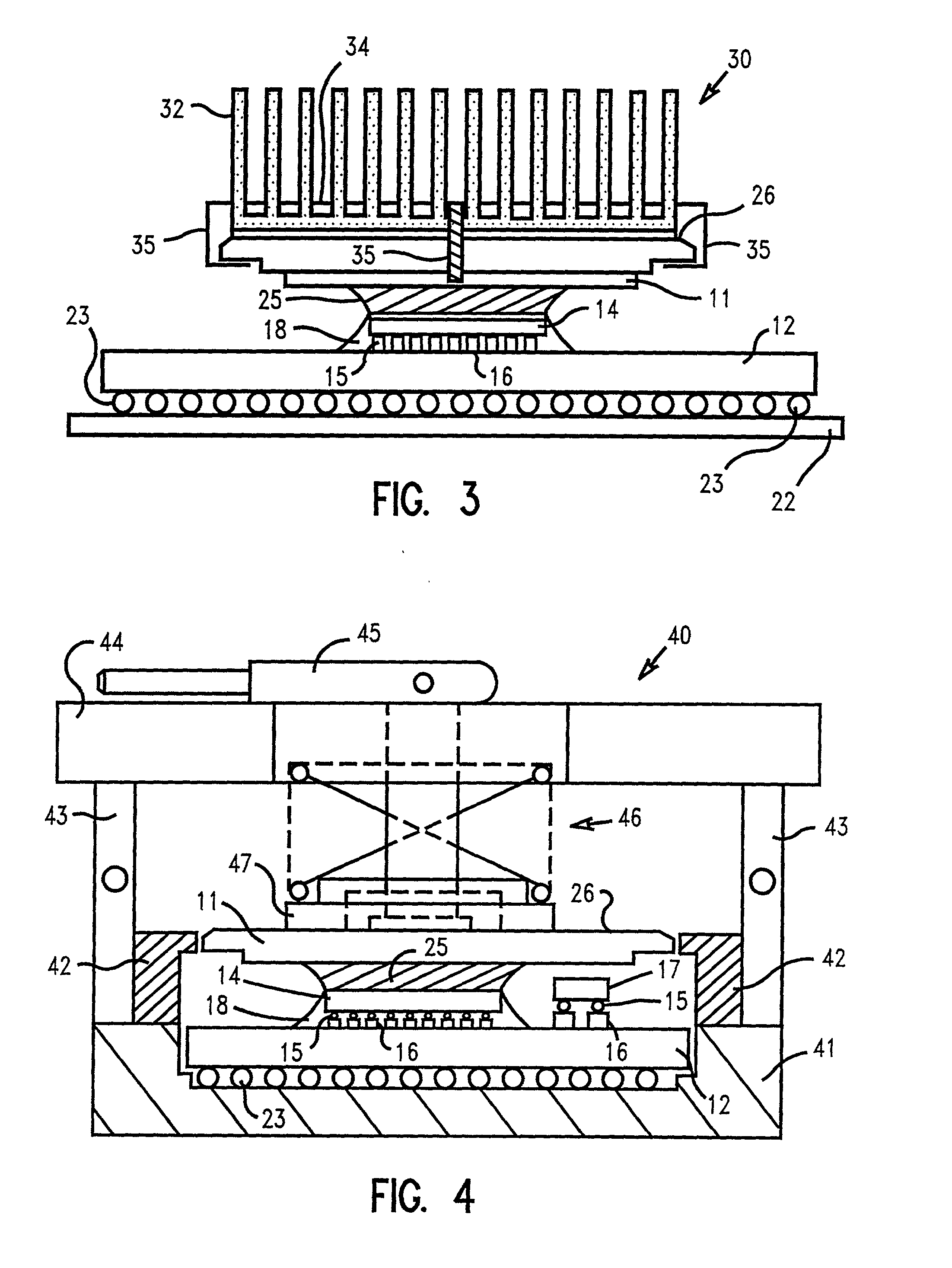

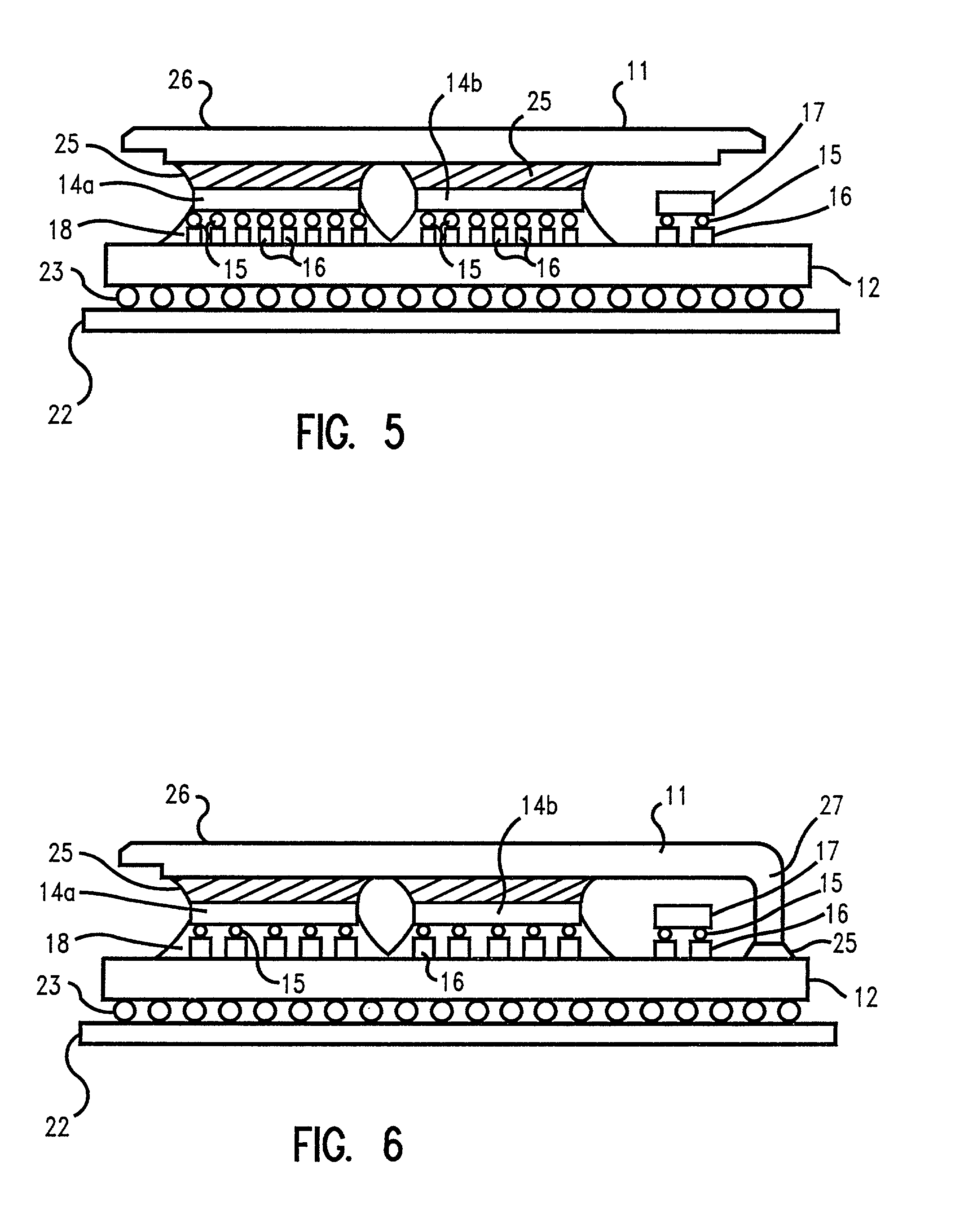

[0035] In describing the preferred embodiment of the present invention, reference will be made herein to FIGS. 1-8 of the drawings in which like numerals refer to like features of the invention. Features of the invention are not necessarily shown to scale in the drawings.

[0036] Designers of ceramic chip carries are under ever increasing pressure to maximize the utilization of available top surface design space to package electronic components, giving the highest regard to cost and space efficiency. This invention describes one way to reduce cost of such packages without any loss or degradation of their performance. Packaging methods which reduce cost advantageously increase the availability of such electronic packages in the marketplace.

[0037] FIG. 2 illustrates a preferred embodiment of the present invention. Ceramic semiconductor chip 14 is connected to substrate 12 by solder balls 15 on pads 16. Chip underfill material 18 encapsulates at least a portion, and preferably all, of s...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Mass | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Electrical conductor | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com