Delay locked loop circuit

A delay-locked loop and phase-delay technology, applied in electrical components, static memory, automatic control of power, etc., can solve problems such as reduced operational reliability of semiconductor memory devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] Hereinafter, memory devices according to specific embodiments of the present invention will be described in detail with reference to the accompanying drawings.

[0034] The semiconductor memory device according to the present invention specifically provides an enhanced delay locked loop (DLL) function.

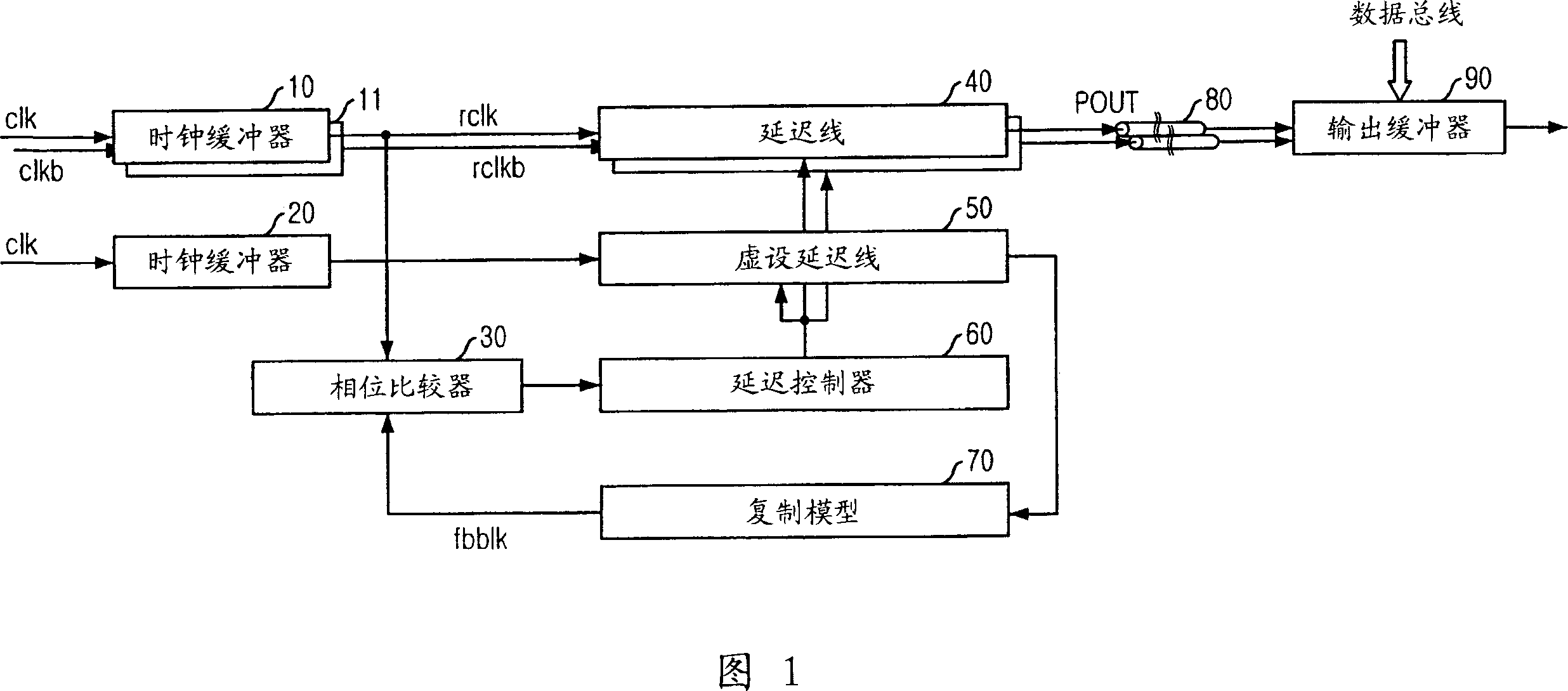

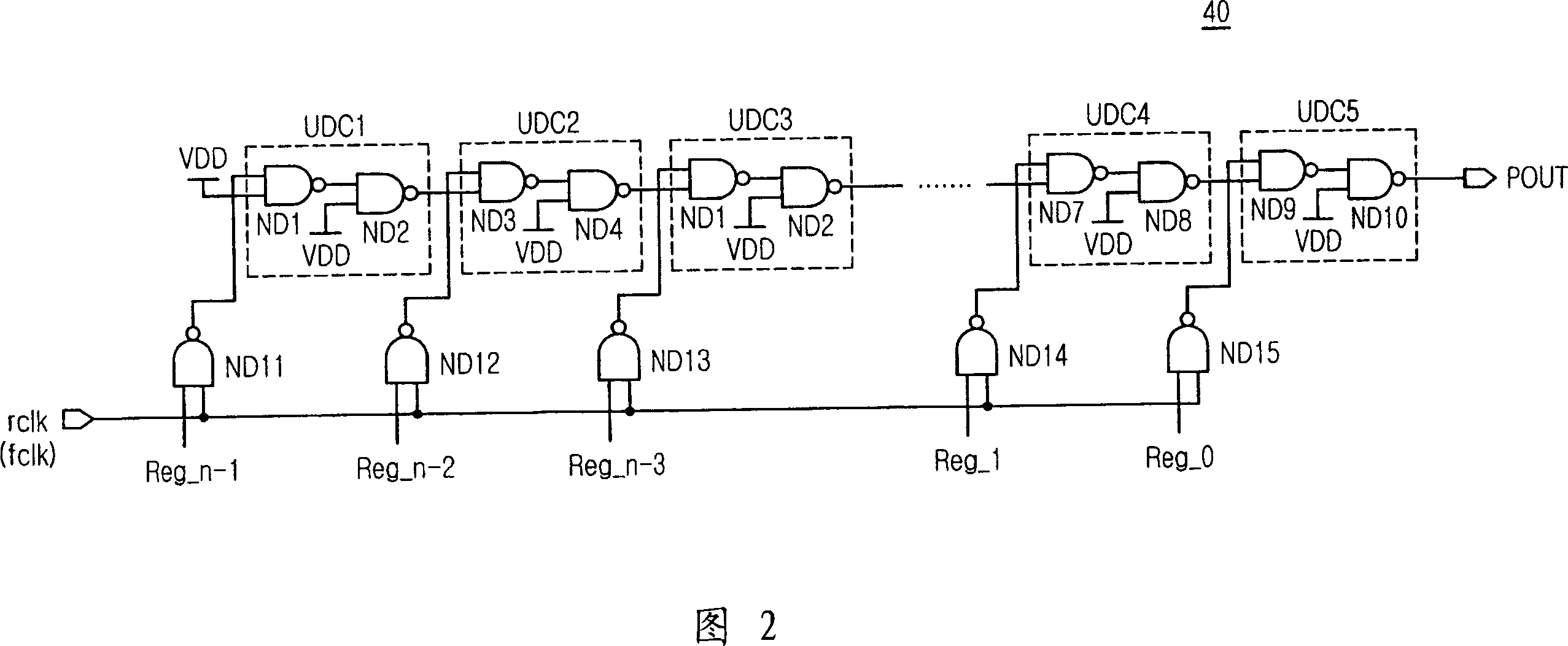

[0035] FIG. 3 is a block diagram illustrating a delay locked loop for use with a semiconductor memory device according to an embodiment of the present invention.

[0036] The delay locked loop includes: a clock delay compensation block, a phase controller 180 and a multi-phase delay controller 130 . The clock delay compensation block includes: clock buffers 100 , 101 and 110 , phase comparator 120 , delay controller 160 , multi-phase delay line 140 , dummy delay line 150 , replica model 170 and output buffer 200 .

[0037] The clock delay compensation block receives external clock signals clk and clkb to generate a first multi-clock MPCLK and a second multi-clock MPOUT...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com