Structure of double-bit mask type only-read memory and its making method

A read-only memory and manufacturing method technology, which is applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve the problems of memory cell interference, easy generation of second-bit effects, and small operating margins, avoiding the Mutual interference, elimination of second-order effects, and improved operating margins

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

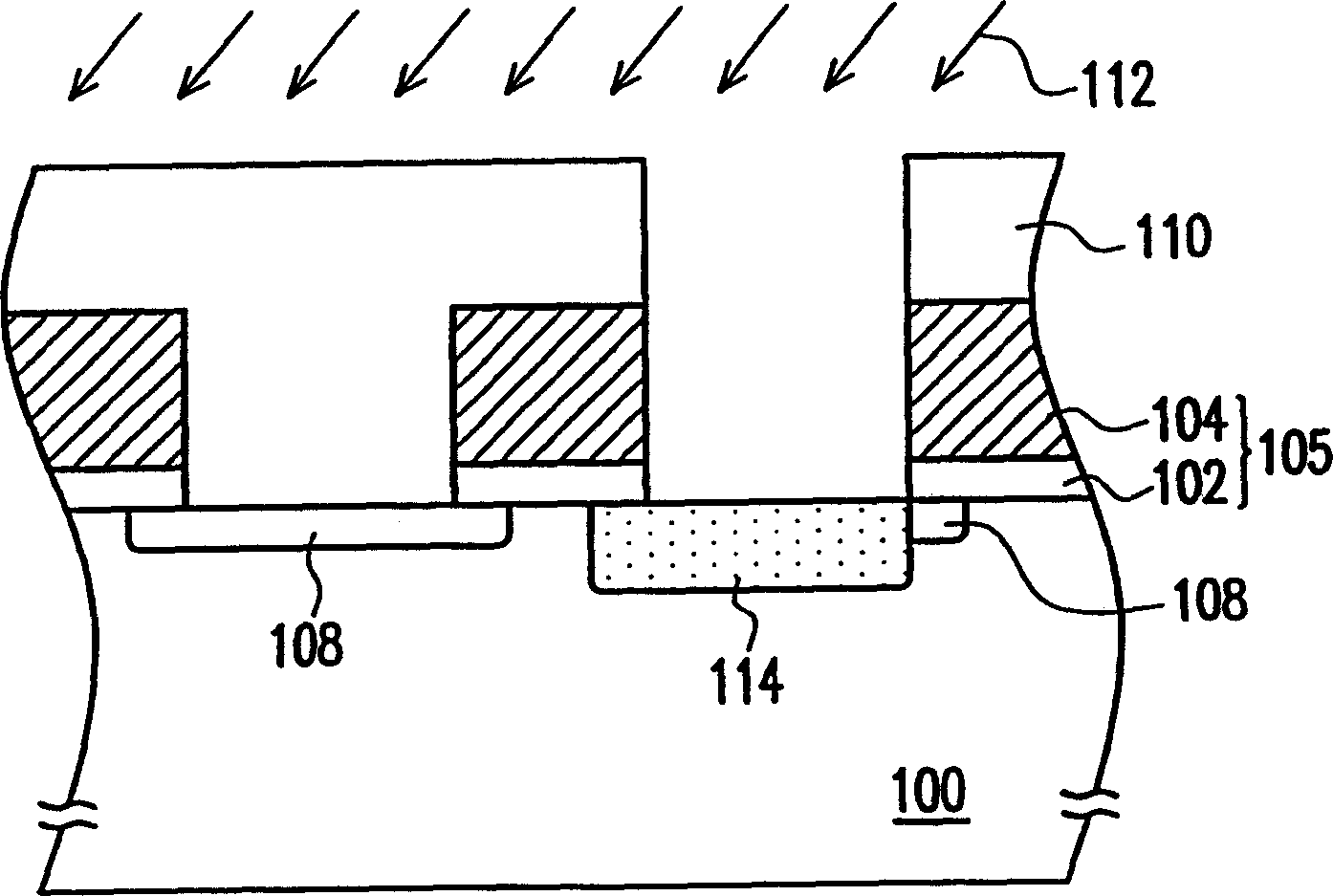

[0027] Figure 2A to Figure 2E , which is a cross-sectional schematic view of the manufacturing process of the dual-bit mask mode ROM according to a preferred embodiment of the present invention.

[0028] Please refer to Figure 2A Firstly, a gate structure 105 is formed on a substrate 100 . Wherein, the gate structure 105 includes a gate conductive layer 104 and a gate oxide layer 102 formed under the gate conductive layer 104 . In this embodiment, the material of the gate conductive layer 104 is, for example, polysilicon, and the thickness of the gate oxide layer 102 is, for example, about 45 angstroms.

[0029] Next, a pocket ion implantation step 106 is performed to form a pocket doped region 108 in the substrate 100 on both sides of the gate structure 105 . In this embodiment, the ions implanted in the pocket-type doped region 108 are, for example, arsenic ions, and an ion implantation dose in the pocket-type ion implantation step 106 is, for example, 1×10 13 / cm 2 A...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com